# Programmable Communication Interface PCI

# FEATURES

- □ Synchronous and Asynchronous Full Duplex or Half Duplex Operations

- Re-programmable ROM on-chip baud rate generator

- Synchronous Mode Capabilities

- Selectable 5 to 8-Bit Characters

- Selectable 1 or 2 SYNC Characters

- Internal Character Synchronization

- Transparent or Non-Transparent Mode

- Automatic SYNC or DLE-SYNC Insertion

- -SYNC or DLE Stripping

- Odd, Even, or No Parity

- Local or remote maintenance loop back mode

- Asynchronous Mode Capabilities

- --- Selectable 5 to 8-Bit Characters --- 3 Selectable Clock Rates (1X, 16X, 64X the

- -3 Selectable Clock Hates (1X, 16X, 64X the Baud Rate)

- Line Break Detection and Generation

- 1, 1½, or 2-Stop Bit Detection and Generation

- False Start Bit Detection

- Odd, Even, or No Parity

- Parity, Overrun, and framing error detect

- Local or remote maintenance loop back mode

- Automatic serial echo mode

- Baud Rates

- DC to 1.0M Baud (Synchronous)

- DC to 1.0M Baud (1X, Asynchronous)

- DC to 62.5K Baud (16X, Asynchronous)

- DC to 15.625K Baud (64X, Asynchronous)

- □ Double Buffering of Data

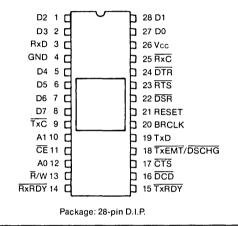

# PIN CONFIGURATION

Internal or External Baud Rate Clock —16 Internal Rates:50 to 19,200 Baud

- □ Single +5 volt Power Supply

- TTL Compatible

- No System Clock Required

- Compatible with 2651, INS2651

The COM 2651 is an MOS/LSI device fabricated using SMC's patented COPLAMOS® technology that meets the majority of asynchronous and synchronous data communication requirements. by interfacing parallel digital systems to asynchronous and synchronous data communication channels while requiring a minimum of processor overhead. The COM 2651 contains a baud rate generator which can be programmed to either accept an external clock or to generate internal transmit or receive clocks. Sixteen different baud rates can be selected under program control when operating in the internal clock mode. The on-chip baud rate generator can be ROM reprogrammed to accommodate different baud rates and different starting frequencies.

The COM 2651 is a Universal Synchronous/

#### **GENERAL DESCRIPTION**

Asynchronous Receiver/Transmitter (USART) designed for microcomputer system data communications. The USART is used as a peripheral and is programmed by the processor to communicate in commonly used asynchronous and synchronous serial data transmission techniques including IBM Bi-Sync. The USART receives serial data streams and converts them into parallel data characters for the processor. While receiving serial data, the USART will also accept data characters from the processor in parallel format, convert them to serial format and transmit. The USART will signal the processor when it has completely received or transmitted a character and requires service. Complete USART status including data format errors and control signals is available to the processor at any time.

99

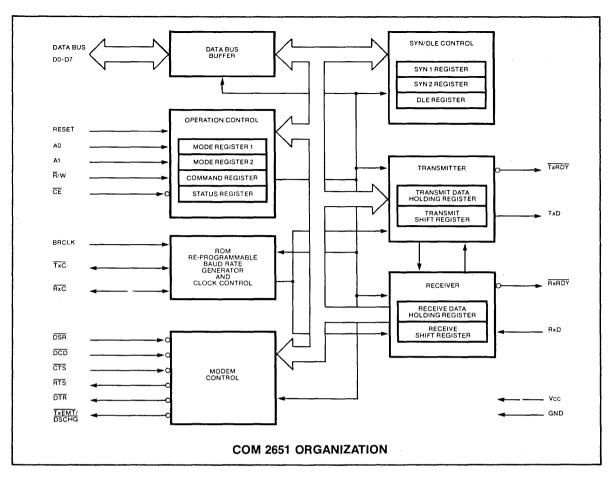

The COM 2651 is organized into 6 major sections. Communication between each section is achieved via an internal data and control bus. The data bus buffer allows a processor access to all internal registers on the COM 2651.

# **Operation Control**

This functional block stores configuration and operation commands from the processor and generates appropriate signals to various internal sections to control the overall device operation. It contains read and write circuits to permit communications with a processor via the data bus and contains Mode Registers 1 and 2, the Command Register, and the Status Register. Details of register addressing and protocol are presented in the COM 2651 programming section of this specification.

# Timing

The COM 2651 contains a Baud Rate Generator (BRG) which is programmable to accept external transmit or receive clocks or to divide an external clock to perform data communications. The unit can generate 16 commonly used baud rates, any one of which can be selected for full duplex operation. Table 6 illustrates all available baud rates.

# Receiver

The Receiver accepts serial data on the RxD pin, converts this serial input to parallel format, checks for bits or characters that are unique to the communication technique and stores the "assembled" character in the receive data holding register until read by the processor.

# Transmitter

The Transmitter accepts parallel data from the processor, converts it to a serial bit stream, inserts the appropriate characters or bits (based on the communication technique) and outputs a composite serial stream of data on the TxD output pin.

# Modem Control

The modem control provides three output signals and accepts three input signals used for "handshaking" and status indication between the COM 2651 and a modem.

# SYN/DLE Control

This section contains control circuitry and three 8-bit registers storing the SYN1, SYN2, and DLE characters provided by the processor. These registers are used in the synchronous mode of operation to provide the characters required for synchronization, idle fill and data transparency.

## Interface Signals

The COM 2651 interface signals can be grouped into two types: the processor-related signals (shown in Table 2) which interface the COM 2651 to the processor, and the device-related signals (shown in Table 3), which are used to interface to the communications equipment.

## TABLE 2—PROCESSOR RELATED SIGNALS

| PIN NO.               | NAME                                    | SYMBOL          | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------|-----------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,2,5,6,<br>7,8,27,28 | Data                                    | D7-DØ           | Bidirectional; 8 bit, three state data bus used to transfer commands, data and status between the COM 2651 and a processor. DØ is the least significant bit; D7 is the most significant bit.                                                                                                                                                                                                                                                                                                                                              |

| 10,12                 | Address                                 | A1, AØ          | Input; Address lines used to select COM 2651 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11                    | Chip Enable                             | ĈĒ              | Input; when this signal is low, the operation specified by the $\overline{R}/W$ , A1 and A0 will be performed. When this input is high, D7-0 are in the high impedance state.                                                                                                                                                                                                                                                                                                                                                             |

| 13                    | Read/Write                              | R∕W             | Input; Processor read/write direction control. This signal defines the direction of the data bus $D7-0$ when the COM 2651 is selected. $D7-0$ drives out (read) when this signal is low and accepts data input when this signal is high. The input only has meaning when the chip enable input is active.                                                                                                                                                                                                                                 |

| 14                    | Receiver Ready                          | RxRDY           | Output; This signal is the complement of Status Register bit 1 (SR1). When low, it indicates that the Receive Data Holding Register (RHR) has a character ready for input to the processor. It goes high when the RHR is read by the processor, and also when the receiver is disabled. It is an open drain output which can be used as an interrupt to the processor.                                                                                                                                                                    |

| 15                    | Transmitter<br>Ready                    | TxRDY           | Output; This signal is the complement of Status Register bit 0 (SR0). When low, it indicates that the Transmit Data Holding Register (THR) is ready to accept a data character from the processor. It goes high when the data character is loaded. This output is valid only when the transmitter is enabled. It is an open drain output which can be used as an interrupt to the processor.                                                                                                                                              |

| 18                    | Transmitter<br>empty/data<br>set change | TxEMT/<br>DSCHG | Output; This signal is the complement of Status Register bit 2 (SR2). When low, it indicates that the transmitter has completed serialization of the last character loaded by the processor, or that a change of state of the DSR or DCD inputs has occurred. This output goes high when the Status Register is read by the processor, if the TxEMT condition does not exist. Otherwise, the THR must be loaded by the processor for this line to go high. It is an open drain output which can be used as an interrupt to the processor. |

| 21                    | Reset                                   | Reset           | Input; A high on this input performs a master reset on the COM 2651. This signal asynchronously terminates any device activity and clears the Mode, Command and Status registers. The device assumes the idle state and remains there until initialized with the appropriate control words.                                                                                                                                                                                                                                               |

| 26                    | Supply Voltage                          | Vcc             | +5 volts supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4                     | Ground                                  | GND             | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# TABLE 3-DEVICE RELATED SIGNALS

| PIN NO. | NAME                   | SYMBOL | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3       | Receive Data           | RxD    | Input; Serial data to the receiver. "Mark" is high "space" is low.                                                                                                                                                                                                                                                                                                                                |

| 9       | Transmitter<br>Clock   | TxC    | Input or Output; If the external transmitter clock is programmed, this input controls the rate at which the character is transmitted. Its frequency is 1X, 16X or 64X, the Baud rate as programmed by Mode Register 1. The transmitted data changes on the falling edge of the clock. If the internal transmitter clock is programmed, this pin becomes an output at 1X the programmed Baud rate. |

| 16      | Data Carrier<br>Detect | DCD    | Input; This signal must be low in order for the receiver to function. The complement appears in the Status Register bit 6 (SR6). When this input changes state a low output on TxEMT/DSCHG occurs.                                                                                                                                                                                                |

| 17      | Clear to Send          | CTS    | Input; This signal must be low in order for the transmitter to function. If it goes high during transmission, the character in the Transmit Shift Register will be transmitted before termination.                                                                                                                                                                                                |

| 19      | Transmit Data          | TxD    | Output; Serial data from the transmitter. "Mark" is high, "Space" is low. This signal is held in the "Mark" condition when the transmitter is disabled.                                                                                                                                                                                                                                           |

| 20      | Baud Rate Clock        | BRCLK  | Input; The standard device requires a 5.0688MHz clock to the internal Baud rate generator allowing for Baud rate shown in Table6. The reprogrammable ROM on chip allows for user specificed Baud rates and input frequency. Consult the factory for details. This input is not required if external receive and transmit clocks are used.                                                         |

| 22      | Data Set Ready         | DSR    | Input; This general purpose signal can be used for Data Set Ready or Ring Indicator condition. Its complement app <u>ears as Status Register bit 7 (SR7). When this input changes state, a low output on TxEMT/DSCHG occurs.</u>                                                                                                                                                                  |

| 23      | Request to Send        | RTS    | Output; This general purpose signal is the complement of the Command Register bit 5 (CR5). It is normally used to indicate Request to Send.                                                                                                                                                                                                                                                       |

#### TABLE 3-DEVICE RELATED SIGNALS

| PIN NO. | NAME          | SYMBOL | FUNCTION                                                                                                                                                                                                                                                                                                                                                                       |

|---------|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24      | Data Terminal | DTR    | Output; This general purpose signal is the complement of the Command Register bit 1 (CR1). It is normally used to indicate Data Terminal Ready.                                                                                                                                                                                                                                |

| 25      | Receive Clock | RxC    | Input or Output; If the external receiver clock is programmed, this input controls the rate at which the character is to be received. Its frequency is 1X, 16X, or 64X the Baud rate, as programmed by Mode Register 1. Data are sampled on the rising edge of the clock. If internal receiver clock is programmed, this pin becomes an output at 1X the programmed Baud rate. |

# COM 2651 OPERATION

The functional operation of the COM 2651 is programmed by a set of control words supplied by the processor. These control words specify items such as synchronous or asynchronous mode, baud rate, number of bits per character, etc. The programming procedure is described in the COM 2651 Programming section of this data sheet.

After programming, the COM 2651 is ready to perform the desired communications functions. The receiver performs serial to parallel conversion of data received from a modem or equivalent device. The transmitter converts parallel data received from the processor to a serial bit stream. These actions are accomplished within the framework specificed by the control words.

## Receiver

The COM 2651 is conditioned to receive data when the DCD input is low and the RxEN bit in the command register is true. In the asynchronous mode, the receiver looks for a high to low transition on the RxD input line indicating the start bit. If a transition is detected, the state of the RxD line is sampled again after a delay of one-half of a bit time. If RxD is now high, the search for a valid start bit is begun again. If RxD is still low, a valid start bit is assumed and the receiver continues to sample the input line at one bit time intervals until the proper number of data bits, the parity bit, and the stop bit(s) have been assembled. The data is then transferred to the Receive Data Holding Register, the RxRDY bit in the status register is set, and the RxRDY output is asserted. If the character length is less than 8 bits, the high order unused bits in the Holding Register are set to zero. The Parity Error, Framing Error, and Overrun Error status bits are strobed into the status register on the positive going edge of RxC corresponding to the received character boundary. If a break condition is detected (RxD is low for the entire character as well as the stop bit[s]), only one character consisting of all zeros (with the Framing error status bit set) will be transferred to the Holding Register. The RxD input must return to a high condition before a search for the next start bit begins.

When the COM 2651 is initialized into the synchronous mode, the receiver first enters the hunt mode on a 0 to 1 transition of RxEN (CR2). In this mode, as data is shifted into the Reciver Shift Register a bit at a time, the contents of the register are compared to the contents of the SYN1 register. If the two are not equal, the next bit is shifted in and the comparison is repeated. When the two registers match, the hunt mode is terminated and character assembly begins. If the single SYN operation is programmed, the SYN DETECT status bit is set. If double SYN operation is programmed, the first character assembled after SYN1 must be SYN2 in order for the SYN DETECT bit to be set. Otherwise, the COM 2651 returns to the hunt mode. (Note that the sequence SYN1-SYN1-SYN2 will not achieve synchronization). When synchronization has been achieved, the COM 2651 continues to assemble characters and transfers them to the Holding Register. The RxRDY status bit is set and the RxRDY output is asserted each time a character is assembled and transferred to the Holding Register. The Overrun error (OE) and Parity error (PE) status bits are set as appropriate. Further receipt of the proper SYN sequence sets the SYN DETECT status bit. If the SYN stripping mode is commanded, SYN characters are not transferred to the Holding Register. Note that the SYN characters used to establish initial synchronization are not transferred to the Holding Register in any case.

## Transmitter

The COM 2651 is conditioned to transmit data when the CTS input is low and the TxEN command register bit is set. The COM 2651 indicates to the processor that it can accept a character for transmission by setting the TxRDY status bit and asserting the TxRDY output. When the processor writes a character into the Transmit Data Holding Register, the TxRDY status bit is reset and the TxRDY output is returned to a high (false) state. Data is transferred from the Holding Register to the Transmit Shift Register when it is idle or has completed transmission of the previous character. The TxRDY conditions are then asserted again. Thus, one full character time of buffering is provided.

In the asynchronous mode, the transmitter automatically sends a start bit followed by the programmed number of data bits, the least significant bit being sent first. It then appends an optional odd or even parity bit and the programmed number of stop bits. If, following transmission of the data bits, a new character is not available in the Transmit Holding Register, the TxD output remains in the marking (high) condition and the TxEMT/DSCHG output and its corresponding status bit are asserted. Transmission resumes when the processor loads a new character into the Holding Register. The transmitter can be forced to output a continuous low (BREAK) condition by setting the Send Break command bit high.

In the synchronous mode, when the COM 2651 is initially conditioned to transmit, the TxD output remains high and the TxRDY condition is asserted until the first character to be transmitted (usually a SYN character) is loaded by the processor. Subsequent to this, a continuous stream of characters is transmitted. No extra bits (other than parity, if commanded) are generated by the COM 2651 unless the processor fails to send a new character to the COM 2651 by the time the transmitter has completed sending the previous character. Since synchronous communication does not allow gaps between characters, the COM 2651 asserts TxEMT and automatically "fills" the gap by transmitting SYN1s, SYN1-SYN2 doublets, or DLE-SYN1 doublets, depending on the state of MR16 and MR17. Normal transmission of the message resumes when a new character is available in the Transmit Data Holding Register. If the SEND DLE bit in the command register is true, the DLE character is automatically transmitted prior to transmission of the message character in the transmit holding register.

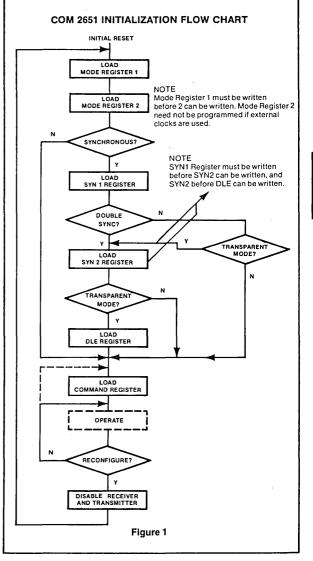

# COM 2651 PROGRAMMING

Prior to initiating data communications, the COM 2651 operational mode must be programmed by performing write operations to the mode and command registers. In addition, if synchronous operation is programmed, the appropriate SYN/DLE registers must be loaded. The COM 2651 can be reconfigured at any time during program execution. However, if the change has an effect on the reception of a character the receiver should be disabled. Alternatively if the change is made 1½ RxC periods after RxRDY goes active it will affect the next character assembly. A flowchart of the initialization process appears in Figure 1.

The internal registers of the COM 2651 are accessed by applying specific signals to the  $\overline{CE}$ ,  $\overline{R}/W$ , A1 and A0 inputs. The conditions necessary to address each register are shown in Table 4.

The SYN1, SYN2, and DLE registers are accessed by performing write operations with the conditions A1=0, A0=1, and R/W=1. The first operation loads the SYN1 register. The next loads the SYN2 register, and the third loads the DLE register. Reading or loading the mode registers is done in a similar manner. The first write (or read) operation addresses Mode Register 1, and a subsequent operation addresses Mode Register 2. If more than the required number of accesses are made, the internal sequencer recycles to point at the first register. The pointers are reeset to SYN1 Register and Mode Register 1 by a RESET input or by performing a "Read Command Register" operation.

The COM 2651 register formats are summarized in Tables 5, 6, 7 and 8. Mode Registers 1 and 2 define the general operational characteristics of the COM 2651, while the Command Register controls the operation within this basic framework. The COM 2651 indicates its status in the Status Register. These registers are cleared when a RESET input is applied.

| CE | A1 | A0 | Ĩ₹/₩ | FUNCTION                        |

|----|----|----|------|---------------------------------|

| 1  | х  | Х  | Х    | Tri-state data bus              |

| 0  | 0  | 0  | 0    | Read receive holding register   |

| 0  | 0  | 0  | 1    | Write transmit holding register |

| 0  | 0  | 1  | 0    | Read status register            |

| 0  | 0  | 1  | 1    | Write SYN1/SYN2/DLE registers   |

| 0  | 1  | 0  | 0    | Read mode registers 1 and 2     |

| 0  | 1  | 0  | 1    | Write mode registers 1 and 2    |

| 0  | 1  | 1  | 0    | Read command register           |

| 0  | 1  | 1  | 1    | Write command register          |

Table 4—COM 2651 REGISTER ADDRESSING

# **MODE REGISTER 1 (MR1)**

Table 5 illustrates Mode Register 1. Bits MR11 and MR10 select the communication format and Baud rate multiplier. 00 specifies synchronous mode and 1X multiplier. 1X, 16X, and 64X multipliers are programmable for asynchronous format. However, the multiplier in asynchronous format applies only if the external clock input option is selected by MR24 or MR25.

MR13 and MR12 select a character length of 5, 6, 7, or 8 bits. The character length does not include the parity bit, if programmed, and does not include the start and stop bits in asynchronous mode.

MR14 controls parity generation. If enabled, a parity bit is added to the transmitted character and the receiver

performs a parity check on incoming data. MR15 selects odd or even parity when parity is enabled by MR14.

In asychronous mode, MR17 and MR16 select character framing of 1, 1.5, or 2 stop bits. (if 1X baud rate is programmed, 1.5, stop bits defaults to 1 stop bits on transmit). In synchronous mode, MR17 controls the number of SYN characters used to establish synchronization and for character fill when the transmitter is idle. SYN1 alone is used if MR17=1, and SYN1-SYN2 is used when MR17=0. If the transparent mode is specified by MR16, DLE-SYN1 is used for character fill and SYN Detect, but the normal synchronization sequence is used. Also DLE stripping and DLE Detect (with MR14=0) are enabled.

| MR17                                                                            | MR16                             | MR15            | MR14                    | MR13             | MR12                                 | MR11        | MR10           |

|---------------------------------------------------------------------------------|----------------------------------|-----------------|-------------------------|------------------|--------------------------------------|-------------|----------------|

| Syr                                                                             | Sync/Async                       |                 | Parity Control          | Character Length |                                      | Mode and Ba | ud Rate Factor |

| ASYNCH: STOP<br>00=INVALID<br>01=1 STOP BIT<br>10=1½ STOP BIT<br>11=2 STOP BITS | rs                               | 0=ODD<br>1=EVEN | 0=DISABLED<br>1=ENABLED | 01=<br>10=       | 5 BITS<br>6 BITS<br>7 BITS<br>8 BITS |             |                |

| SYNCH: NUMBEI<br>OF SYN CHAR                                                    | SYNCH: TRANS-<br>PARENCY CONTROL |                 |                         |                  |                                      |             |                |

| 0=DOUBLE SYN<br>1=SINGLE SYN                                                    | 0=NORMAL<br>1=TRANSPARENT        |                 |                         |                  |                                      |             |                |

NOTE Baud rate factor in asynchronous applies only if external clock is selected. Factor is 16X if internal clock is selected. Mode must be selected (MR11, MR10) in any case.

TABLE 5-MODE REGISTER 1(MR1)

# **MODE REGISTER 2 (MR2)**

Table 6 illustrates Mode Register 2. MR23, MR22, MR21, and MR20 control the frequency of the internal Baud rate generator (BRG). Sixteen rates are selectable. When driven by a 5.0688 MHz input at the BRCLK input (pin 20), the BRG output has zero error except at 134.5, 2000, and 19,200 Baud, which have errors of  $\pm 0.016\% \pm 0.253\%$ , and  $\pm 3.125\%$  respectively.

inputs TxC and RxC as the clock source for the transmitter and receiver, respectively. If the BRG clock is selected, the Baud rate factor in asynchronous mode is 16X regardless of the factor selected by MR11 and MR10. In addition, the corresponding clock pin provides an output at 1X the Baud rate. Custom Baud rates other than the ones provided by the standard part are available. Contact the factory for details.

MR25 and MR24 select either the BRG or the external ab

| MR27 | MR26 | MR25                 | MR24              |      |              | MR23                                  | 3-MR20                           |                  |         |

|------|------|----------------------|-------------------|------|--------------|---------------------------------------|----------------------------------|------------------|---------|

|      |      | Transmitter<br>Clock | Receiver<br>Clock | Code | Baud<br>Rate | Theoretical<br>Frequency<br>16X Clock | Actual<br>Frequency<br>16X Clock | Percent<br>Error | Divisor |

|      |      | 0=EXTERNAL           | 0=EXTERNAL        | 0000 | 50           | 0.8 KHz                               | 0.8 K Hz                         | _                | 6336    |

| NOT  | USED | 1=INTERNAL           | 1=INTERNAL        | 0001 | 75           | 1.2                                   | 1.2                              |                  | 4224    |

|      |      |                      |                   | 0010 | 110          | 1.76                                  | 1.76                             | - 1              | 2880    |

|      |      |                      |                   | 0011 | 134.5        | 2.152                                 | 2.1523                           | 0.016            | 2355    |

|      |      |                      |                   | 0100 | 150          | 2.4                                   | 2,4                              | -                | 2112    |

|      |      |                      |                   | 0101 | 300          | 4.8                                   | 4.8                              |                  | 1056    |

|      |      |                      |                   | 0110 | 600          | 9.6                                   | 9.6                              | -                | 528     |

|      |      |                      |                   | 0111 | 1200         | 19.2                                  | 19.2                             | -                | 264     |

|      |      |                      |                   | 1000 | 1800         | 28.8                                  | 28.8                             | - 1              | 176     |

|      |      |                      |                   | 1001 | 2000         | 32.0                                  | 32.081                           | 0.253            | 158     |

|      |      |                      |                   | 1010 | 2400         | 38.4                                  | 38.4                             | -                | 132     |

|      |      |                      |                   | 1011 | 3600         | 57.6                                  | 57.6                             |                  | 88      |

|      |      |                      |                   | 1100 | 4800         | 76.8                                  | 76.8                             | -                | 66      |

|      |      |                      |                   | 1101 | 7200         | 115.2                                 | 115.2                            | - 1              | 44      |

|      |      |                      |                   | 1110 | 9600         | 153.6                                 | 153.6                            | 1 -              | 33      |

|      |      |                      |                   | 1111 | 19200*       | 307.2                                 | 316.8                            | 3.125            | 16      |

NOTE \*Error at 19200 can be reduced to zero by using crystal frequency 4.9152MHz

16X clock is used in asynchronous mode. In synchronous mode, clock multiplier is 1X.

Baud rates are valid for crystal frequency = 5.0688MHz

# COMMAND REGISTER (CR)

Table 7 illustrates the Command Register. Bits CRO (TxEN) and CR2 (RxEN) enable or disable the transmitter and receiver respectively. A 0 to 1 transition of CR2 forces start bit search (async mode) or hunt mode (sync mode) on the second RxC rising edge. Disabling the receiver causes RxRDY to go high (inactive). If the transmitter is disabled, it will complete the transmission of the character in the Transmit Shift Register (if any) prior to terminating operation. The TxD output will then remain in the marking state (high) while the TxRDY and TxEMT will go high (inactive). If the receiver is disabled, it will terminate operation immediately. Any character being assembled will be neglected.

In asynchronous mode, setting CR3 will force and hold the TxD output low (spacing condition) at the end of the current transmitted character. Normal operation resumes when CR3 is cleared. The TxD line will go high for at least one bit time before beginning transmission of the next character in the Transmit Data Holding Register. In synchronous mode, setting CR3 causes the transmission of the DLE register contents prior to sending the character in the Transmit Data Holding Register. CR3 should be reset in response to the next TxRDY.

Setting CR4 causes the error flags in the Status Register (SR3, SR4, and SR5) to be cleared. This is a one time command. There is no internal latch for this bit.

The COM 2651 can operate in one of four sub-modes within each major mode (synchronous or asynchronous). The operational sub-mode is determined by CR7 and CR6. CR7-CR6=00 is the normal mode, with the transmitter and receiver operating independently in accordance with the Mode and Status Register instructions.

In asynchronous mode, CR7-CR6=01 places the COM 2651 in the Automatic Echo mode. Clocked, regenerated received data is automatically directed to the TxD line while normal receiver operation continues. The receiver must be enabled (CR2=1), but the transmitter need not be enabled. Processor to receiver communications continues normally, but the processor to transmitter link is disabled. Only the first character of a break condition is echoed. The TxD output will go high until the next valid start is detected. The following conditions are true while in Automatic Echo mode:

- 1. Data assembled by the receiver are automatically placed in the Transmit Holding Register and retransmitted by the transmitter on the TxD output.

- The transmitter is clocked by the receive clock.

3. TxRDY output=1.

4. The TxEMT/DSCHG pin will reflect only the data set change condition.

### The TxEN command (CR0) is ignored.

In synchronous mode, CR7-CR6=01 places the COM 2651 in the Automatic SYN/DLE Stripping mode. The exact action taken depends on the setting of bits MR17 and MR16:

- 1. In the non-transparent, single SYN mode (MR17-MR16=10), characters in the data stream matching SYN1 are not transferred to the Receive Data Holding Register (RHR).

- 2. In the non-transparent, double SYN mode (MR17-MR16=00), characters in the data stream matching, SYN1, or SYN2 if immediately preceded by SYN1, are not transferred to the RHR. However, only the first SYN1 of an SYN1-SYN1 pair is stripped.

- 3. In transparent mode (MR16=1), characters in the data stream matching DLE, or SYN1 if immediately preceded by DLE, are not transferred to the RHR. However, only the first DLE of a DLE-DLE pair is stripped.

Note that Automatic Stripping mode does not affect the setting of the DLE Detect and SYN Detect status bits (SR3 and SR5).

Two diagnostic sub-modes can also be configured. In Local Loop Back mode (CR7-CR6=10), the following loops are connected internally:

- 1. The transmitter output is connected to the receiver input.

- 2. DTR is connected to DCD and RTS is connected to CTS.

- The receiver is clocked by the transmit clock.

- 4. The DTR, RTS and TxD outputs are held high.

- 5. The CTS, DCD, DSR and RxD inputs are ignored.

Additional requirements to operate in the Local Loop Back mode are that CR0 (TxEN), CR1 (DTR), and CR5 (RTS) must be set to 1. CR2 (RxEN) is ignored by the COM 2651.

The second diagnostic mode is the Remote Loop Back mode (CR7-CR6=11). In this mode:

- 1. Data assembled by the receiver is automatically placed in the Transmit Holding Register and retransmitted by the transmitter on the TxD output.

- The transmitter is clocked by the receive clock.

- 3. No data are sent to the local processor, but the error

- status conditions (PE, OE, FE) are set. 4. The RxRDY, TxRDY, and TxEMT/DSCHG outputs are held high.

- 5. CR0 (TxEN) is ignored.

- All other signals operate normally.

| CR7                                 | CR6               | CR5                                       | CR4                                | CR3                          | CR2                       | CR1                                       | CR0                        |  |

|-------------------------------------|-------------------|-------------------------------------------|------------------------------------|------------------------------|---------------------------|-------------------------------------------|----------------------------|--|

| Opera                               | ting Mode         | Request to<br>Send                        | Reset Error                        | Sync/Async                   | Receive<br>Control (RxEN) | Data Terminal<br>Ready                    | Transmit<br>Control (TxEN) |  |

| 00=NORMAL                           | OPERATION         |                                           | 0=NORMAL                           | ASYNCH:<br>FORCE BREAK       |                           |                                           |                            |  |

|                                     | DDE<br>SYN AND/OR | 0=FORCE RTS<br>OUTPUT HIGH<br>1=FORCE RTS | 1=RESET<br>ERROR FLAG<br>IN STATUS | 0=NORMAL<br>1=FORCE<br>BREAK | 0=DISABLE<br>1=ENABLE     | 0=FORCE DTR<br>OUTPUT HIGH<br>1=FORCE DTR | 0=DISABLE<br>1=ENABLE      |  |

| DLE STRI<br>10=LOCAL L<br>11=REMOTE |                   | OUTPUT LOW                                | (FE, OE,<br>PE/DLE DETECT)         | SYNCH:<br>SEND DLE           |                           | OUTPUT LOW                                |                            |  |

|                                     |                   |                                           |                                    | 0=NORMAL<br>1=SEND DLE       |                           |                                           |                            |  |

The data contained in the Status Register (as shown in Table 8) indicate receiver and transmitter conditions and modem/data set status.

SR0 is the Transmitter Ready (TxRDY) status bit. It, and its corresponding output, are valid only when the transmitter is enabled. If equal to 0, it indicates that the Transmit Data Holding Register has been loaded by the processor and the data has not been transferred to the Transmit Shift Register. If set equal to 1, it indicates that the Holding Register is ready to accept data from the processor. This bit is initially set when the Transmitter is enabled by CR0, unless a character has previously been loaded into the Holding Register. It is not set when the Automatic Echo or Remote Loop Back modes are programmed. When this bit is set, the TxRDY output pin is low. In the Automatic Echo and Remote Loop Back modes, the output is held high.

SR1, the Receiver Ready (RxRDY) status bit, indicates the condition of the Receive Data Holding Register. If set, it indicates that a character has been loaded into the Holding Register from the Receive Shift Register and is ready to be read by the processor. If equal to zero, there is no new character in the Holding Register. This bit is cleared when the processor reads the Receive Data Holding Register or when the receiver is disabled by CR2. When set, the RxRDY output is low.

The TxEMT/DSCHG bit, <u>SR2</u>, when set, indicates either a change of state of the <u>DSR</u> or <u>DCD</u> inputs or that the Transmit Shift Register has completed transmission of a character and no new character has been loaded into the Transmit Data Holding Register. Note that in synchronous mode this bit will be set even though the appropriate "fill" character is transmitted. TxEMT will not go active until at least one character has been transmitted. It is cleared by loading the Transmit Data Holding Register. The DSCHG condition is enabled when TxEN = 1 or RxEN = 1. It is cleared when the Status Register is read by the processor. When SR2 is set, the TxEMT/DSCHG output is low.

SR3, when set, indicates a received parity error when parity is enabled by MR14. In synchronous transparent mode (MR16=1), with parity disabled, it indicates that a character matching the DLE Register has been received. However, only the first DLE of two successive DLEs will set SR3. This bit is cleared when the receiver is disabled and by the Reset Error command, CR4.

The Overrun Error status bit, SR4, indicates that the previous character loaded into the Receive Holding Register was not read by the processor at the time a new received character was transferred into it. This bit is cleared when the receiver is disabled and by the Reset Error command, CR4.

In asynchronous mode, bit SR5 signifies that the received character was not framed by the programmed number of stop bits. (if 1.5 stop bits are programmed, only the first stop bit is checked.) If the RHR contains all 0's when SR5=1, a break condition is present. In synchronous non-transparent mode (MR16=0), it indicates receipt of the SYN1 character in single SYN mode or the SYN1-SYN2 pair in double SYN mode. In synchronous transparent mode (MR16=1), this bit is set upon detection of the initial synchronizing characters (SYN1 or SYN1-SYN2) and, after synchronization has been achieved, when a DLE-SYN1 pair is received. The bit is reset when the receiver is disabled, when the Reset Error command is given in asynchronous mode, or when the Status Register is read by the processor in the synchronous mode.

SR6 and SR7 reflect the conditions of the DCD and DSR inputs respectively. A low input sets the corresponding status bit and a high input clears it.

| SR7                                                                      | SR6                                               | SR5                                                                                       | SR4                            | SR3                                                                                                               | SR2                                                                                         | SR1                                                                       | SR0                                                                     |

|--------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Data Set<br>Ready                                                        | Data Carrier<br>Detect                            | FE/SYN Detect                                                                             | Overrun                        | PE/DLE Detect                                                                                                     | TxEMT/DSCHG                                                                                 | RxRDY                                                                     | TxRDY                                                                   |

| 0= <del>DSR</del> INPUT<br>IS HIGH<br>1= <del>D</del> SR INPUT<br>IS LOW | 0= DCD INPUT<br>IS HIGH<br>1= DCD INPUT<br>IS LOW | ASYNCH:<br>0=NORMAL<br>1=FRAMING<br>ERROR<br>SYNCH:<br>0=NORMAL<br>1=SYN CHAR<br>DETECTED | 0=NORMAL<br>1=OVERRUN<br>ERROR | ASYNCH:<br>0=NORMAL<br>1=PARITY<br>ERROR<br>SYNCH:<br>0=NORMAL<br>1=PARITY<br>ERROR<br>OR<br>DLE CHAR<br>RECEIVED | 0=NORMAL<br>1=CHANGE<br>IN DSR OR<br>DCD, OR<br>TRANSMIT<br>SHIFT REGIS-<br>TER IS<br>EMPTY | 0=RECEIVE<br>HOLDING REG<br>EMPTY<br>1=RECEIVE<br>HOLDING REG<br>HAS DATA | 0=TRANSMIT<br>HOLDING<br>REG BUSY<br>1=TRANSMIT<br>HOLDING<br>REG EMPTY |

TABLE 8-STATUS REGISTER (SR)

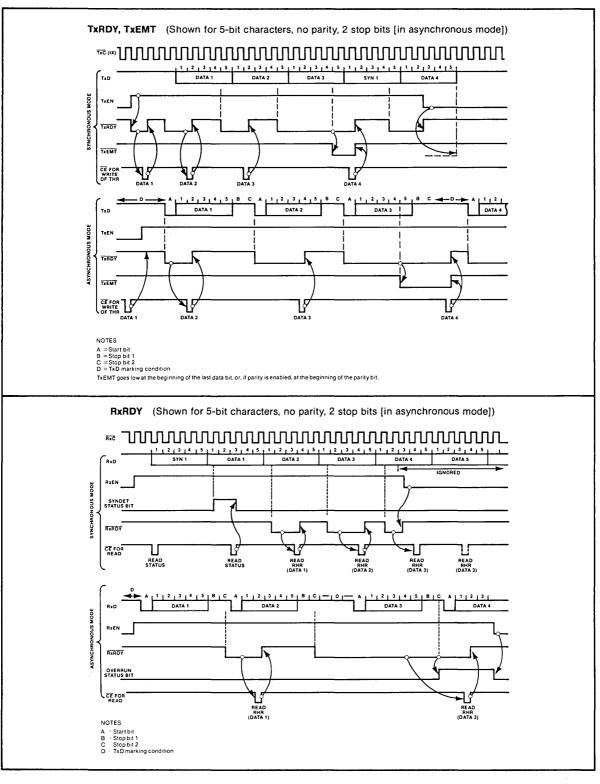

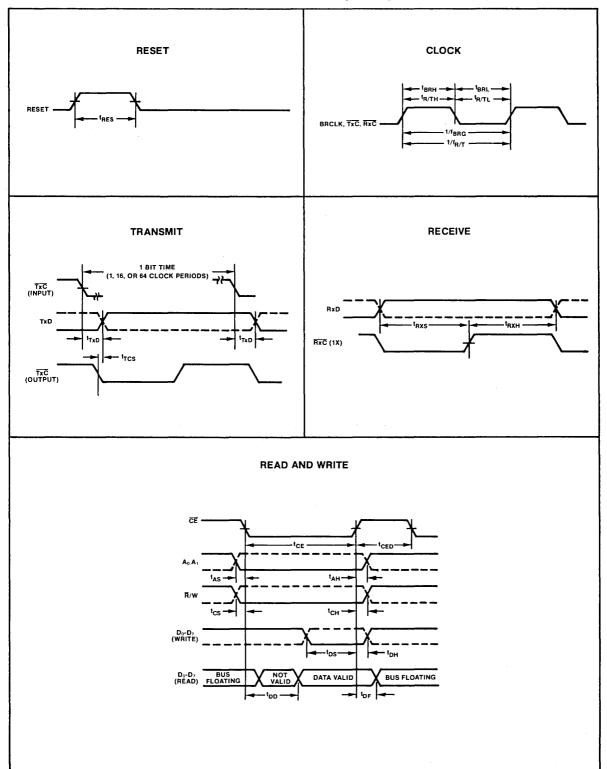

# TIMING DIAGRAMS

SECTION III

#### **MAXIMUM GUARANTEED RATINGS\***

| Operating Temperature Range0°C                      | to + 70°C   |

|-----------------------------------------------------|-------------|

| Storage Temperature Range                           | ; to +150°C |

| Lead Temperature (soldering, 10 sec.)               | +325°C      |

| Positive Voltage on any Pin, with respect to ground | +18.0V      |

| Negative Voltage on any Pin, with respect to ground | –0.3V       |

|                                                     |             |

\*Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

NOTE: When powering this device from laboratory or system power supplies, it it important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes or "glitches" on their outputs when the AC power is switched on and off. In addition, voltage transients on the AC power line may appear on the DC output. For example, the bench power supply programmed to deliver +12 volts may have large voltage transients when the AC power is switched on and off. If this possibility exists it is suggested that a clamp circuit be used.

## DC ELECTRICAL CHARACTERISTICS $T_A=0^{\circ}C$ to $+70^{\circ}C$ , $V_{CC}=5.0V \pm 5\%$

|                        | PARAMETER                                               | MIN | ТҮР | MAX      | UNIT     | TEST CONDITIONS                                   |

|------------------------|---------------------------------------------------------|-----|-----|----------|----------|---------------------------------------------------|

| V <sub>IL</sub><br>Vih | Input voltage<br>Low<br>High                            | 2.0 |     | 0.8      | V        |                                                   |

| V <sub>ol</sub><br>Voh | Output voltage<br>Low<br>High                           | 2.4 |     | 0.4      | V        | I <sub>оL</sub> =1.6mA<br>I <sub>он</sub> =-100µА |

| l <sub>it</sub>        | Input leakage current                                   |     |     | 10       | μA       | V <sub>IN</sub> =0 to 5.25V                       |

| l <sub>lH</sub><br>lu  | Output leakage current<br>Data bus high<br>Data bus low |     |     | 10<br>10 | μΑ<br>μΑ | V <sub>o</sub> =4.0V<br>V <sub>o</sub> =0.45V     |

| lcc                    | Power supply current                                    |     |     | 150      | mA       |                                                   |

| CIN                    | Capacitance<br>Input                                    |     |     | 20       | pF       | fc=1MHz                                           |

| Cout                   | Output                                                  |     |     | 20       | pF       | Unmeasured pins tied                              |

| C <sub>I/O</sub>       | Input/Output                                            |     |     | 20       | рF       |                                                   |

AC ELECTRICAL CHARACTERISTICS  $T_A=0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{cc}=5.0V \pm 5\%$

|                                                                               | PARAMETER                                                                                                                                                                     | MIN                                      | ТҮР    | MAX           | UNIT                                               | TEST CONDITIONS                                            |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------|---------------|----------------------------------------------------|------------------------------------------------------------|

| t <sub>RES</sub><br>t <sub>CE</sub>                                           | Pulse width<br>Reset<br>Chip enable                                                                                                                                           | 1000<br>300                              |        |               | ns<br>ns                                           |                                                            |

| tas<br>tah<br>tcs<br>tch<br>tds<br>tdh<br>trxs<br>taxh                        | Setup and hold time<br>Address setup<br>Address hold<br>R/W control setup<br>R/W control hold<br>Data setup for write<br>Data hold for write<br>Rx data setup<br>Rx data hold | 20<br>20<br>20<br>225<br>0<br>300<br>350 |        |               | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns |                                                            |

| t <sub>DD</sub><br>t <sub>DF</sub><br>t <sub>CED</sub>                        | Data delay time for read<br>Data bus floating time<br>for r <u>ea</u> d<br>CE to CE delay                                                                                     | 700                                      |        | 250<br>150    | ns<br>ns<br>ns                                     | C <sub>L</sub> =100pF<br>C <sub>L</sub> =100pF             |

| f <sub>вRG</sub><br>f <sub>R/T</sub>                                          | Input clock frequency<br>Baud rate generator<br>TxC or RxC                                                                                                                    | 1.0<br>dc                                | 5.0688 | 5.0738<br>1.0 | MHz<br>MHz                                         |                                                            |

| t <sub>ван</sub><br>t <sub>вас</sub><br>t <sub>в/тн</sub><br>t <sub>в/т</sub> | Clock width<br>Baud rate high<br>Baud rate low<br>TxC or RxC high<br>TxC or RxC low                                                                                           | 70<br>70<br>500<br>500                   |        |               | ns<br>ns<br>ns<br>ns                               | f <sub>вяс</sub> =5.0688MHz<br>f <sub>вяс</sub> =5.0688MHz |

| t <sub>TXD</sub><br>t <sub>TCS</sub>                                          | TxD delay from falling<br>edge of TxC<br>Skew between TxD<br>changing and falling                                                                                             |                                          |        | 650           | ns                                                 | C <sub>L</sub> =100pF                                      |

|                                                                               | edge of TxC output                                                                                                                                                            |                                          | 0      |               | ns                                                 | C <sub>L</sub> =100pF                                      |

NOTE:

1.  $f_{\text{B,T}}$  and  $t_{\text{B,TL}}$  shown for all modes except Local Loopback. For Local Loopback mode

f<sub>B/T</sub>=0.7 MHz and t<sub>B/TL</sub>=700ns min.

35 Marcus Bivd. Hauppauge, N.Y. 11786 (516) 273-3100 TWX-510-227-8898 We keep ahead of our competition so you can keep ahead of yours.

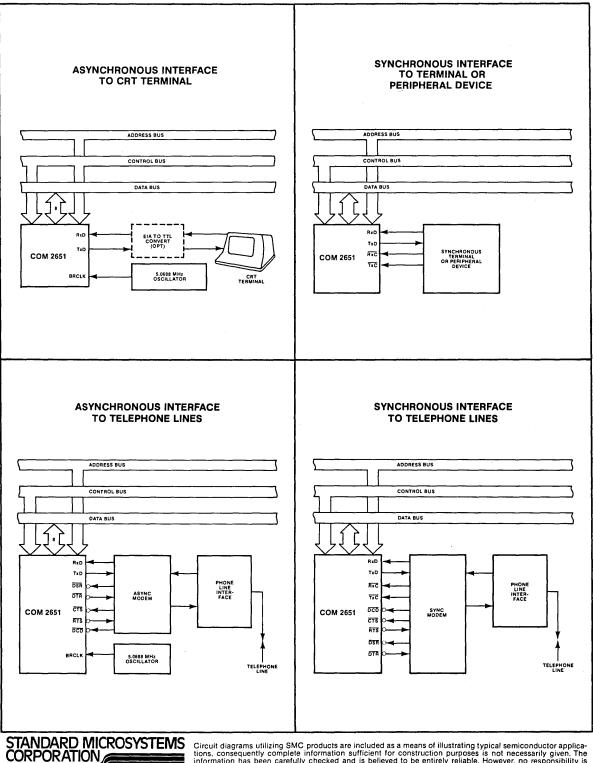

Circuit diagrams utilizing SMC products are included as a means of illustrating typical semiconductor applications, consequently complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey the purchaser of the semiconductor devices described any license under the patent rights of SMC or others. SMC reserves the right to make changes at any time in order to improve design and supply the best product possible.