mikroelektronik

elektronik-bauelemente

APPLIKATIVE INFORMATION

**IWT**

3/1988

# APPLIKATIVE INFORMATION

- für Anwender der Mikroelektronik -

# hinweise

Alle Beiträge in den Heften der "Applikativen Information" dienen der Anregung bei Schaltungs- und Geräteentwicklungen bzw. beim Finden von Rationalisierungslösungen und vor allem dem Erfahrungsaustausch. Es können keine Verbindlichkeiten des VEB Applikationszentrum Elektronik Berlin zur Bereitstellung der in den Beiträgen vorgestellten elektronischen Bauelemente abgeleitet werden.

Grundlage dafür sind die Listen für elektronische Bauelemente und Bausteine, die über die Bauelemente-Verantwortlichen der Betriebe beim VEB Applikationszentrum Elektronik Berlin angefordert werden können.

Reproduktionen in irgendeiner Form durch Druck, Kopienherstellung,

Microfiche u. a. sind nur nach vorheriger schriftlicher Zustimmung des

Herausgebers gestattet. Auszüge, Referate und Besprechungen müssen die

volle Quellenangabe enthalten.

# inhalt ai

# 03/88

Anwenderspezifische integrierte Schaltkreise, Teil 1

|                                                                                | Seite |

|--------------------------------------------------------------------------------|-------|

| Vorwort                                                                        | 3     |

| Anwenderspezifische integrierte Schaltkreise                                   | 5     |

| Integrierte Schaltungsanordnungen aus dem<br>VEB Halbleiterwerk Frankfurt/Oder | 18    |

| Anwenderspezifische Schaltkreise – Methoden zur okonomischen Bewertung         | 24    |

| ISA-Schaltkreis AK 317 D, Eigenschaften und Anwendung                          | 33    |

herausgeber

veb applikationszentrum elektronik berlin im veb kombinat mikroelektronik

- abt. applikative information mikroelektronik -

mainzer str. 25

berlin

1 0 3 5

## Vorwort

Die Mikroelektronik hat sich weltweit zu einem revolutionären Element des wissenschaftlichtechnischen Fortschritts entwickelt. Ihre gesellschaftliche Bedeutung ergibt sich aus den großen, in ihr vorhandenen Potenzen zur Intensivierung der Volkswirtschaft wie

- Einsparung menschlicher Arbeitskraft und effektivere Nutzung des verfügbaren gesellschaftlichen Arbeitsvermögens

- sparsamere Verwendung von Energie, Material und Rohstoffen

- Erhöhung der Zuverlässigkeit großer, komplexer Produktionsanlagen

- entscheidende Verbesserung der Kommunikationssysteme

- Schaffung leistungsfähiger Informationsverarbeitungssysteme.

Die Mikroelektronik durchdringt somit zunehmend die ganze Volkswirtschaft und wird zu einem bestimmenden Faktor für das Niveau der verschiedensten Erzeugnisse und Verfahren. Vor allem deshalb müssen leistungsbestimmende Baugruppen mehr und mehr von den Finalproduzenten selbst hergestellt werden – wie Genosse Erich Honecker auf dem XI. Parteitag der SED feststellte. Zulieferungen, die den Gebrauchswert eines Erzeugnisses bestimmen, müssen Bestandteil der Fertigungspalette der Anwender werden, um den Erneuerungsprozeβ im notwendig hohen Tempo und der erforderlichen Qualität zu beherrschen.

Die anhaltenden Entwicklungstendenzen der Mikroelektronik, die sich voll und ganz mit den volkswirtschaftlichen Erfordernissen decken, werden durch solche Faktoren charakterisiert wie

- steigender Integrationsgrad und zunehmende Komplexität der integrierten elektronischen Funktionen bei sinkenden Kosten

- wachsende Geschwindigkeit bei der Verarbeitung elektrischer Signale (Daten)

- sinkender Energie- und Materialaufwand pro elektronisches Funktionselement.

Entwicklung der Mikroelektronik bedeutet aber auch, daß der Entwurf und die Produktionsvorbereitung eines hochintegrierten Schaltkreises mit zunehmendem Integrationsgrad immer aufwendiger wird. Dieser wachsende Aufwand ist volkswirtschaftlich nur vertretbar, wenn auch große Mengen der entwickelten Schaltkreise produziert werden.

Darüber hinaus besteht ein wichtiger Zusammenhang zwischen der Komplexität eines technischen Systems und der möglichen Nutzung. Je komplexer ein System ist, um so geringer ist die Zahl der möglichen Anwendungen, die genau von diesem System realisiert werden können. Je höher also der Integrationsgrad und die Komplexität eines konkreten Chips sind, um so geringer ist die Anwendungsbreite der auf diesem Chip integrierten Schaltung.

Die Lösung dieses "Widerspruchs" der Mikroelektronik erfordert, die notwendige Anjaussung eines integrierten Schaltkreises an ein zu lösendes technisches Problem mit solchen Mitteln zu erreichen, die vom Anwender mitbestimmt und weitestgehend selbst, entsprechend den konkret vorliegenden individuellen Erfordernissen, verwirklicht werden können.

Eine solche "Individualisierung" der technischen Problemanpassung der Mikroelektronik mit "standardisierten" und in großen Stückzahlen produzierten mikroelektronischen Bauelementen läßt sich sowohl durch unspezifische Hardware mittels Speicherprogrammierung (softwaregesteuerte Mikroprozessoren) als auch durch anwenderspezifische Schaltkreise realisieren.

Eine wesentliche Voraussetzung für die breite Nutzung von anwenderspezifischen Schaltkreisen ist die jetzt verfügbare rechnergestützte Entwurfstechnik einschließlich der notwendigen technologischen Grundlagen (CAD/CAM-Systeme).

Die effektive Nutzung dieses Weges, der es auch Anwendern mit kleinen Bauelemente-Stückzahlen ermöglicht, die Vorteile der Mikroelektronik auszuschöpfen, erfordert allerdings vom Anwender ein tiefes Eindringen und Beherrschen der schaltungstechnischen Gesamtlösung, die Beherrschung der Entwurfstechnologie und -normative u. a. bis zur Entwicklung des integrationsfähigen Gsamtkonzepts.

Gleichzeitig ergeben sich völlig neue Anforderungen an die Gestaltung der Verantwortungsabgrenzung zwischen dem Bauelementehersteller und -anwender für den Schaltungsentwurf und Fertigungsprozeß.

Inzwischen wurden erste produktionswirksame Ergebnisse bei dieser sich neu herausbildenden Arbeitsteilung zwischen Bauelementeherstellerbetrieben und Anwenderkombinaten erzielt. Sie kommen der kostengünstigen und schnellen Realisierung von anwenderspezifischen Schaltkreisen zugute. Damit wurde ein Prozeß eingeleitet, der die Effektivität vieler Anwenderlösungen, zum Beispiel auf dem Gebiet der Steuerungen und Regelungseinrichtungen für viele technologische Prozesse, Be- und Verarbeitugsmaschinen u. a. steigert. Anwenderspezifische Schaltkreise werden damit mehr und mehr zum Ausgangspunkt einer grundlegenden Erneuerung vieler Erzeugnisse, bestimmen zu einem wesentlichen Teil das Niveau und die Absatzfähigkeit der Warenproduktion in den Anwenderkombinaten und beeinflussen entscheidend die Dynamik des Wachstums unserer Volkswirtschaft.

Mit den nachfolgenden Beiträgen in diesem und folgenden Heften wird ein Überblick über anwenderspezifische Schaltkreise wie

- ISA-Schaltkreise

- Gate-Arrays

- Standardzellen-Schaltkreise

in der DDR gegeben.

Die Vermittlung der bei der Entwicklung, Einsatzvorbereitung und Anwendung gesammelten Erfahrungen, insbesondere auch für Anwender der Mikroelektronik in Klein- und Mittelbetrieben, wird dazu beitragen, die Vorzüge der Mikroelektronik zunehmend auch in diesem Bereich zu nutzen.

Dr. Heise

Betriebsdirektor des VEB Applikationszentrum Elektronik Berlin Ing., Dipl.-Ük. Erhard Haupt Dipl.-Ing., Dr. oec. Heinrich Heise

> VEB Applikationszentrum Elektronik Berlin im VEB Kombinat Mikroelektronik

## Anwenderspezifische integrierte Schaltkreise

Es wird eine Gesamtübersicht über den Stand der Einführung von anwenderspezifischen integrierten Schaltkreisen (ASIC = application specific integrated circuits) und ihrer Anwendung in der Volkswirtschaft gegeben. Der Artikel beinhaltet nicht spezielle technische Bewertungen der durch die Bauelementehersteller bereitzustellenden Systeme, da dies bereits ausführlich in der Fachliteratur erfolgte bzw. durch die nachfolgenden Fachartikel geschehen wird. Die folgenden Ausführungen sollen insbesondere diejenigen Interessenten ansprechen, die als Erstanwender von ASIC in Frage kommen und mit diesem Beitrag eine Orientierung zum Gesamtprozeß ASIC erhalten.

#### 1. Anwendung, Einteilung und Merkmale anwenderspezifischer Schaltkreise

Mit dem weiteren Vordringen der Mikroelektronik und insbesondere der Mikrorechentechnik in breiteste volkswirtschaftliche Bereiche – dabei ist nur an solche Industriezweige wie den Textil- und Werkzeugmaschinenbau zu denken – wachsen die Anforderungen an die Flexibilität und Problemanpaßbarkeit mikroelektronischer Bauelemente. Mit dem vorhandenen Standardsortiment an Mikroprozessoren, Speichern und Logikschaltkreisen können dabei ca. 90 ... 95 % der Anwenderforderungen abgedeckt werden. Die restlichen 5 ... 10 % betreffen individuelle Schaltungslösungen, die neben den speziellen technischen Forderungen auch noch durch kleine Stückzahlen zwischen 1 000 und 10 000 Stück gekennzeichnet sind.

Der erreichte Stand der Produktionstechnologie der Bauelementehersteller und in der Methodik des Schaltkreisentwurfs einschließlich der stürmischen Entwicklung entsprechender Entwurfsrechentechnik (CAD/CAM) führte dazu, daß für diese Anwendungsfälle ein Schaltkreisangebot in Form der anwenderspezifischen Schaltkreise, durch die Bauelementehersteller international seit den 80er Jahren bereitgestellt wird. Durch große volkswirtschaftliche Effekte, wie Senkung des Material- und Arbeitszeitaufwandes, Erhöhung der Zuverlässigkeit und erhebliche Reduzierung der Entwicklungszeit und der Entwicklungskosten gewinnen ASIC eine ständig zunehmende Bedeutung.

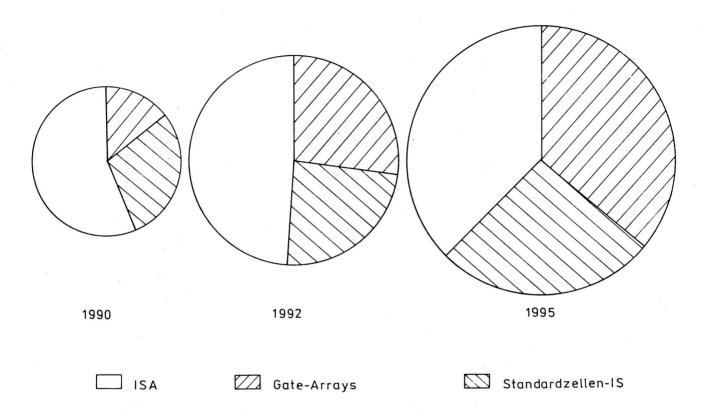

International wird eingeschätzt, daß ASIC in den 90er Jahren auf dem kapitalistischen Weltmarkt den gleichen Marktanteil wie Standardschaltkreise haben werden. Dabei werden sich innerhalb der anwenderspezifischen Schaltkreise die Produktionsanteile, wie in Tabelle 1 dargestellt, entwickeln.

Tabelle 1: Entwicklung der Produktionsanteile von ASIC (in %) /10/

| ASIC                        | 1984 | 1988 | 1990 |  |

|-----------------------------|------|------|------|--|

| Vollkunden-Schaltkreise     | 47   | 25   | 20   |  |

| Standardzellen-Schaltkreise | 6    | 25   | 35   |  |

| Gate-Arrays                 | 32   | 30   | 30   |  |

| PLD                         | 15   | 15   | 15   |  |

|                             |      |      |      |  |

Als bestimmende Technologie setzt sich dabei die CMOS-Technologie mit folgenden Vorteilen durch:

- geringer Leistungsverbrauch

- gute Logikpegel und damit Reduzierung der Schnittstellenprobleme

- hohe Zuverlässigkeit

- geringe Störanfälligkeit.

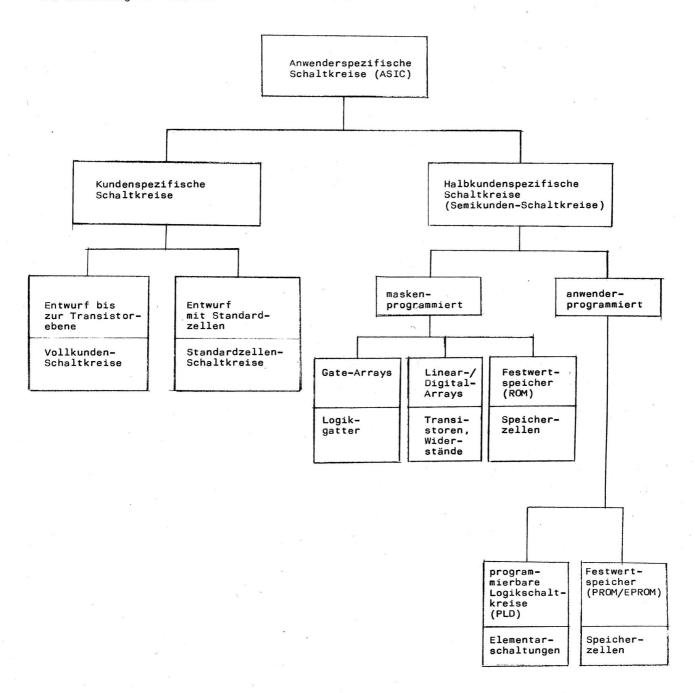

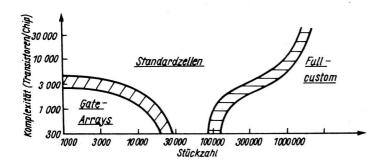

Die Einteilung der ASIC ist im Bild 1 enthalten.

Bild 1: Übersicht über die verschiedenen Kategorien anwenderspezifischer Schaltkreise (ASIC)

#### 1.1. Vollkunden-Schaltkreise

Vollkunden-Schaltkreise werden in allen Entwurfsschritten individuell nach den speziellen Kundenforderungen durch den Bauelementehersteller entwickelt und produziert. Es erfolgt eine Optimierung der gesamten Entwurfs- und Herstellungsprozesse hinsichtlich des Aufbaus und der Anordnung der einzelnen Funktionselemente.

Kennzeichnend ist eine hohe Ausnutzung der Chipfläche, ein hoher Integrationsgrad, große Stückzahlen bei zeit- und kostenaufwendigen Entwicklungsprozessen.

#### 1.2. Standardzellen-Schaltkreise

Standardzellen-Schaltkreise gehen von einem Zellenkatalog aus, der bereits entworfene und erprobte Grundschaltungen (Standardzellen) enthält, die nach dem Baukastenprinzip kombiniert werden können.

In der Zellenbibliothek befinden sich die Daten für das funktionelle Verhalten (Logik), die schaltungstechnischen Parameter und die konstruktiven Eigenschaften von einfachen Logikschaltungen bis zu größeren Logikkomplexen. Nach einem Softwareprogramm entwirft der Anwender auf der Basis dieser Zellenbibliothek seine Schaltung, einschließlich Plazierung und Verdrahtung der einzelnen Standardzellen auf dem Chip.

Im Herstellungsprozeß müssen beim Bauelementehersteller alle technologischen Einzelschritte einschließlich der dazugehörigen Schablonenfertigung durchlaufen werden. Dies erhöht die Aufwendungen und Kosten und amortisiert sich erst bei höheren Stückzahlen. Kennzeichnend ist eine Verminderung des Entwicklungsrisikos, da mit fehlerfreien Standardzellen entwickelt wird, sowie eine hohe Ausnutzung und Optimierung der Chipfläche.

#### 1.3. Gate-Arrays

Gate-Arrays sind Schaltkreise, bei denen auf einem einheitlichen vorgefertigten Schaltkreisuntergrund (Master) eine oder mehrere Verdrahtungsebenen nach spezifischer Anforderung durch den Anwender realisiert werden können. Der Anwender entwirft seine spezifische funktionelle Schaltung auf der Grundlage eines durch den Bauelementehersteller vorgegebenen Makrokatalogs, der die logischen Grundelemente enthält. Die anwenderspezifische Lösung erfolgt mit den freiprogrammierbaren Verdrahtungsebenen auf der Grundlage der leistungsfähigen Entwurfssoftware.

Das CAD-System übernimmt dabei die Plazierung der Makros, verdrahtet sie (Trassierung) und führt den Layoutentwurf der anwenderspezifischen Ebene aus.

Am Ende des Entwurfsprozesses des Bauelementeanwenders werden die Magnetbänder für die Schablonenherstellung der anwenderspezifischen Ebene (Patterngenerator), für den Plotter und den Tester ausgegeben. Damit sind die Voraussetzungen gegeben, im Produktionsbereich des Bauelementeherstellers im Zyklus J dem Anwenderentwurf entsprechende Schaltkreise zu präparieren.

Diese Technik gestattet damit – auf einem bereits im Scheibenverband mit großen Stückzahlen vorgefertigten Chip – die individuelle kurzfristige Anpassung. Um den Schaltkreis zu fertigen, müssen nur die anwenderspezifischen Ebenen bei Bereitstellung der entsprechenden Schablonen gefertigt werden.

#### 1.4. Programmierbare Logikschaltkreise

Programmierbare Logikschaltkreise (PLD) sind vom Bauelementehersteller vorgefertigte Schaltkreise die vom Anwender programmiert werden. Sie stellen den schnellsten Weg zur Realisierung individueller Lösungen dar, die jedoch im Einsatz durch die Höhe des Integrationsgrades und die Komplexität begrenzt sind. Die vom Hersteller gelieferten programmierbaren Logikschaltkreise enthalten in Matrixform angeordnete gleichartige Schaltungen, die durch rechnergesteuertes Ausbrennen der Leitungsverbindungen anwenderspezifisch angepaßt werden. Damit ist eine Unabhängigkeit von technologischen Prozessen des Bauelementeherstellers z. B. Maskenherstellung gegeben.

Tabelle 2: Merkmale verschiedener Realisierungsmöglichkeiten eines Anwenderproblems mittels integrierter Schaltkreise

| 9 | Merkmal                                                   | Einheit | Logikschalt-<br>kreise<br>(Standard-<br>schaltkreise | Schaltkreise | Standard-<br>zellen-<br>Schaltkreise | Gate-Arrays | Pro-<br>grammier-<br>bare<br>Logik-<br>schalt-                   |

|---|-----------------------------------------------------------|---------|------------------------------------------------------|--------------|--------------------------------------|-------------|------------------------------------------------------------------|

| _ |                                                           |         |                                                      |              |                                      |             | kreise<br>(Schmelz-<br>program-<br>mierbare<br>Logik-<br>Arrays) |

|   | - Entwicklungskosten                                      | Faktor  | 1                                                    | 1,5          | 0,3 0,4                              | 0,1 0,2     | 0,1                                                              |

| - | Entwicklungsdauer bis<br>zum Prototyp                     |         | 1 3 a                                                | 1 3 a        | 2 6 Mon.                             | 1 3 Mon.    | (<1 Mon.)<br>(bzw.<br>einige<br>h)                               |

| _ | · Umfang des Schaltungs                                   |         |                                                      |              |                                      |             |                                                                  |

|   | entwurfes durch den<br>Anwender                           | %       | 100                                                  | 100          | 70                                   | 20          | 10                                                               |

| - | Vorfertigung beim<br>Bauelementehersteller                | %       | 100                                                  | 0 ,          | 0                                    | 80 90       | 100                                                              |

| - | kundenspezifische<br>Masken <sup>1</sup>                  | Anzahl  | -                                                    | 8 12         | 8 12                                 | 1 3         | -                                                                |

| - | Chipfläche                                                | Faktor  | 1                                                    | 1            | 1,2 1,5                              | 1,7 2,2     | 2                                                                |

| - | Ausnutzung der Chip-<br>fläche                            | %       | 100                                                  | 100          | 80 90                                | 60 70       | 50                                                               |

| - | ökon. Mindestmenge                                        | T Stück | 500                                                  | 75 100       | 10 30                                | 1 10        | ab 1 St.                                                         |

| - | Komplexität (typische<br>durchschnittliche<br>Gatterzahl) |         | bis 25 000                                           | bis 50 000   | bis 80 000                           | bis 10 000  | 100                                                              |

|   | Flexibilität der<br>Schaltkreise                          |         | gering                                               | sehr hoch    | hoch                                 | mittel hoch | gering mittel                                                    |

| - | Änderungsfreundlich-<br>keit des Gerätekon-<br>zeptes     | a e     | mittel                                               | gering       | gering                               | mittel      | hoch                                                             |

| - | Kosten bei Geräte-<br>änderungen                          |         | mittel                                               | sehr hoch    | hoch                                 | hoch        | gering                                                           |

Anm.: 1 abhängig von der gewählten Technologie

Die Anwendung von PLD gewinnt damit für Anwender mit kleinen Stückzahlen zunehmend an Bedeutung.

Unabhängig von der Architektur gliedern sich die PLD in die Gruppen der

- einmalig programmierbaren PLD

- mehrmalig oder auch löschbaren PLD, den sogenannten EPLD

Die verschiedenen Realisierungsmöglichkeiten mit ihren Vor- und Nachteilen lassen sich, wie in Ta- belle 2 dargestellt, bewerten.

#### 2. Anwenderspezifische Schaltkreise der DDR

Ableitend aus dem internationalen Trend wurden in der DDR Entscheidungen getroffen, um eigene Systemlösungen zu entwickeln und parallel dazu beim Anwender personelle und materielle Entwurfskapazitäten aufzubauen.

Für die Anwenderindustrie steht folgendes Angebot an erprobten anwenderspezifischen Schaltkreisen bereit.

#### 2.1. ISA-System

Als bipolare integrierte Schaltungsanordnungen stehen vier digitale bzw. digital/analoge Grundchips ID 40 ... ID 70 zur Verfügung.

Der weitestgehend automatisierte Schaltungsentwurf wird mit Hilfe des Entwurfssystems "ISA CAD" realisiert.

Hauptanwendungsgebiete des ISA-Systems: Nachrichtenelektronik, optischer und wissenschaftlicher Gerätebau.

#### 2.2. Gate-Array-System

Das System U 5200 bietet Schaltkreise für digitale Anwendungen (Gatterverzögerungszeit 5 ns).

Für den Schaltungsentwurf steht das Entwurfssystem "Archimedes" zur Verfügung.

Hauptanwendungsgebiete des Systems U 5200: Rechentechnik, wissenschaftlicher Gerätebau, Nachrichtenelektronik, Geräte der Audio-/Videotechnik, Prozeßautomatisierung, Werkzeugmaschinenbau.

### 2.3. Standardzellen-System

Das System U 1500/U 1520 bietet Schaltkreise für digitale Anwendungen (Gatterverzögerungszeit 6 ns).

Für den Schaltungsentwurf dienen automatische Verfahren.

Hauptanwendungsgebiete des Systems U 1500/U 1520: Rechentechnik, Nachrichtenelektronik, Werk-zeugmaschinenbau.

#### 2.4. Realisierte Schaltkreise

Anhand der technisch-ökonomischen Parameter (Tabelle 3) und des derzeitigen Anwendungsstandes ist zu erkennen, daß das Gate-Array-System für die DDR das derzeitig bestimmende System ist, mit dem kurzfristig die vielfältigsten Schaltungslösungen realisiert werden können.

Auf der Grundlage der genannten ASIC-Systeme steht zur Zeit ein Sortiment (Schaltkreise mit Produktionsfreigabe) von

- 16 ISA-Schaltkreisen

- 10 Gate-Arrays (U 5200)

- 7 Standardzellen-Schaltkreisen (U 1500/U 1520)

#### bereit.

Im Jahr 1987 wurden darüber hinaus 51 Schaltkreisentwürfe (davon 38 Gate-Arrays und zehn Standardzellen-Schaltkreise) realisiert, von denen 28 Schaltkreise (davon 23 Gate-Arrays und drei Standardzellen-Schaltkreise) als Prototypen präpariert werden und das ASIC-Sortiment 1988/89 erweitern. Aus diesen Zahlen wird eine für die kurze Zeit nach der Produktionseinführung hohe Dynamik der Anwendung von Gate-Arrays und Standardzellen-Schaltkreisen sichtbar.

Tabelle 3: Vergleich der Systeme anwenderspezifischer Schaltkreise der DDR

| Merkmal                                                                     | ISA-System                                                        | Gate-Array-<br>System U 5200                  | Standardzellen-<br>System U 1500/<br>U 1520 |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------|

| Technologie                                                                 | bipolar/I <sup>2</sup> L                                          | CMOS/CSGT 2                                   | CMOS/CSGT 2                                 |

| Schaltungsart                                                               | analog/digital                                                    | digital                                       | digital                                     |

| Integrationsgrad<br>(Transistoren/Chip)                                     | 10 <sup>3</sup> (analoge Anw.)<br>10 <sup>4</sup> (bipolare Anw.) | 12 000                                        | max. 13 000                                 |

| Layout                                                                      | feste Elementeanord-<br>nung und variable<br>Verbindungsmuster    | für jeweiliges<br>Grundmaster fest-<br>gelegt | kundenspezifisch                            |

| Bereitstellungszeitraum für<br>Musterpräparation (Prototyp)<br>(in Monaten) | 3                                                                 | ≦ 3                                           | ≦ 6                                         |

| ökonomische Mindestmenge pro<br>Jahr (TStck)                                | max. 10                                                           | 1 10                                          | 10 30                                       |

| Gehäuse                                                                     | DIL 16 und DIL 18                                                 | QCP 68                                        | QCP 68 und<br>DIP 16 40                     |

| Aufwandsverhältnis be-<br>züglich Entwicklungszeit<br>und Kosten            | 1,5                                                               | 1                                             | 2                                           |

| Einsparung von SSI-/MSI-<br>Schaltkreisen pro einge-<br>setzten ASIC        | 10                                                                | 20 50                                         | bis 50                                      |

| Durchschnittliche Ein-<br>sparung in M pro einge-<br>setzten ASIC           | 300,                                                              | 1 600,                                        | 2 000,                                      |

| Chipfläche (mm²)                                                            | 15,6 24                                                           | 52,5                                          | 13 56                                       |

Eine Sortimentsübersicht der wichtigsten bisher mit Produktionsfreigabe realisierten anwenderspezifischen Schaltkreise der DDR ist in Tabelle 4 enthalten.

Tabelle 4: Sortimentsübersicht anwenderspezifischer Schaltkreise der DDR 1987 (Arbeitsstand 9/87)

| Тур                   | Funktionsbeschreibung         | Einsatzgebiet                |

|-----------------------|-------------------------------|------------------------------|

| 1.1. ISA-Schaltkreise | <u>.</u>                      |                              |

| KA 601 D              | PCM-IS                        | Nachrichtentechnik           |

| KA 602 D              | PCM-IS                        | Nachrichtentechnik           |

| KA 605 D              | Zweitonkanal-IS               | Fernsehrundfunkempfänger     |

| KA 305 D              | Zweitonkanal-IS               | Fernsehrundfunkempfänger     |

| KA 610 D              | V 10-Schnittstellen-IS        | Nachrichtenelektronik        |

| KA 615 X              | Stromquellen-IS               | Nachrichtenelektronik        |

| KA 620 D              | IS für Lichtleiterübertragung | Nachrichtenelektronik        |

| KA 621 D              | IS für Lichtleiterübertragung | Automatisierungstechnik      |

| KA 625 G              | Kamera-IS                     | Kameras                      |

| KA 628 D              | Kamera-IS                     | Kameras                      |

| KA 630 D              | ZF-IS                         | Nachrichtenelektronik        |

| KD 310 D              | Steuer-IS                     | Nachrichtenelektronik        |

| KD 311 D              | Steuer-IS                     | Nachrichtenelektronik        |

| KD 320 D              | Fehlerortungs-IS              | Nachrichtenelektronik        |

| IA 338 D              | Funktionsgenerator            | Nachrichtenelektronik        |

| ID 170 D              | Teiler-/Zähler-IS             | Nachrichtenelektronik        |

| 1.2. Gate-Arrays      |                               |                              |

| U 5201 PC-103         | IEC-Bus-Controller            | Wissenschaftlicher Gerätebau |

| U 5201 PC-105         | Messelektronik-IS             | Automatisierungstechnik      |

| U 5201 PC-107         | Fernsehimpulsgeber            | Nachrichtenelektronik        |

| U 5201 PC-108         | Fernsehimpulsgeber            | Nachrichtenelektronik        |

| U 5201 PC-111         | Floppy-Steuerung              | Rechentechnik                |

| U 5201 PC-112         | D/A-Wandler                   | Textilmaschinenbau           |

| J 5201 PC-114         | Treiber/Sensor                | wissenschaftlicher Geräteba  |

| J 5201 PC-115         | Taxibordcomputer              | Verkehrswesen                |

| U 5201 PC-301         | Belichtungsautomatik          | Kameras                      |

| U 5201 PC-302         | Serielles Interface           | wissenschaftlicher Geräteba  |

| 1.3. Standardzellen-S | Schaltkreise                  |                              |

| U 1500 PC-001         | PCM-Sender                    | Nachrichtenelektronik        |

| U 1500 PC-002         | PCM-Empfänger                 | Nachrichtenelektronik        |

| U 1500 PC-003         | IS für Lichtleiterübertragung | Nachrichtenelektronik        |

| U 1500 PC-004         | Steuerwerk-IS                 | Werkzeugmaschinenbau         |

| U 1500 PC-050         | Teilnehmer-IS                 | Nachrichtenelektronik        |

| U 1520-PC-002         | IS für KC 90                  | Rechentechnik                |

| U 1520 PC-003         | IS für KC 90                  | Rechentechnik                |

# 3. Arbeitsteilige Zusammenarbeit zwischen Bauelementeherstellern und -anwendern

Wie bereits die Begriffsbestimmungen und Einteilung der ASIC-Schaltkreise zeigen, ist eine neue Qualität der Zusammenarbeit zwischen Bauelementehersteller und -anwender bei der Entwicklung von ASIC-Schaltkreisen dahingehend erforderlich, daß der Anwender Mitwirkungsleistungen bei der Entwicklung von Bauelementen realisieren muß. Der Einsatz anwenderspezifischer Schaltkreise wird eine wichtige Anwendungsrichtung der Mikroelektronik und die damit verbundene Schaltkreisentwicklung ein Kernstück der jeweiligen Applikationstätigkeit des Bauelementeanwenders. Damit werden sich folgende Arbeitsteilungen künftig herausbilden:

- von den Bauelementeherstellern werden Technologien, Standardschaltkreise sowie Schaltkreise mit komplizierten technologischen Randbedingungen einschließlich der ASIC-Systeme mit ihrer Entwurfssoftware entwickelt

- die Geräteindustrie übernimmt auf der Basis gesicherter Technologien bei Anwendung entsprechender materieller eigener bzw. genutzter Entwurfstechnik und durch die Bauelementehersteller bereitgestellter Entwurfssoftware die Eigenentwicklung von ASIC.

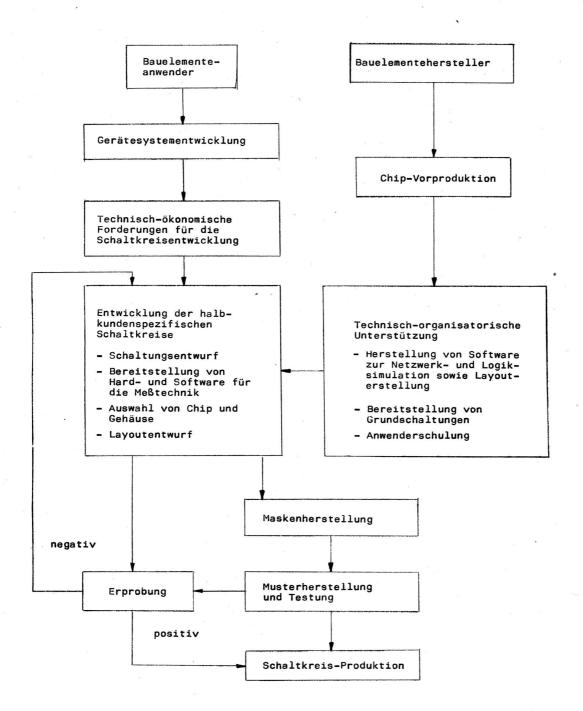

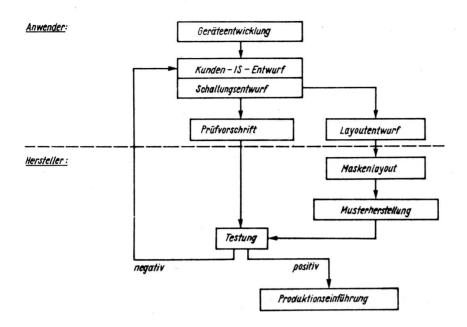

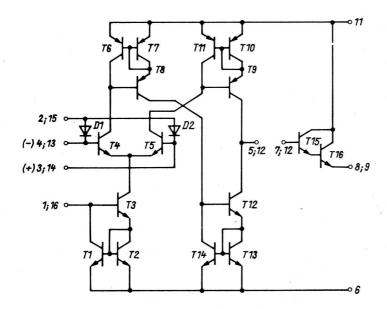

Durch den Bauelementeanwender sind auf der Grundlage der bereitstehenden ASIC-Systemunterlagen folgende grundlegenden Arbeitsschritte am Beispiel der Gate-Array-Systems durchzuführen:

- ableitend aus der Gerätesystementwicklung erfolgt der Systementwurf mit den technisch-ökonomischen Forderungen für die Schaltkreisentwicklung und mit der Festlegung der Wahl der ASIC-Variante

- auf der Grundlage der Entwurfssoftware mit den festgelegten Entwurfsregeln, des Makrokatalogs und der bereitstehenden Master erfolgt ein erster Logik-Entwurf

- es erfolgt die Umsetzung des Logikentwurfs in eine rechnerspezifische Sprache (Netzwerk-Beschreibungs-Sprache NBS) als Voraussetzung für die Nutzung des Gate-Array-CAD-Systems. Mit Hilfe dieses Systems erfolgt über die Plazierung, Trassierung der Makros und entsprechender Simulationsprogramme der Layoutentwurf; ein spezielles Programmsystem erzeugt automatisch die Testfolgen für den Tester

- die erzeugten Magnetbanddaten für den Plotter und den Patterngenerator sind die Voraussetzung für die Maskenherstellung und die folgende Präparation der Master beim Bauelementehersteller.

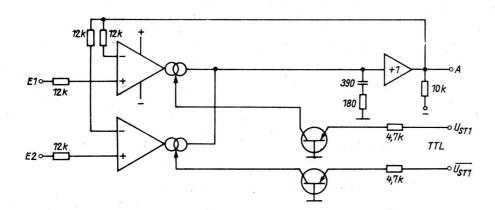

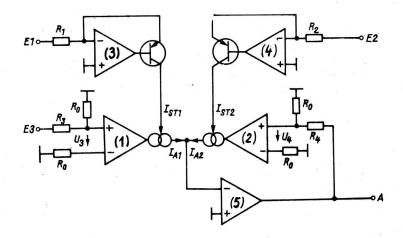

Dieser Arbeitsablauf mit den daraus entstehenden Kooperationsbeziehungen und der Arbeitsteilung zwischen Bauelementehersteller und -anwender wird im Bild 2 verdeutlicht.

Zur Umsetzung der sich aus dieser Arbeitsteilung ergebenden neuen wissenschaftlich-technischen Anforderungen zu eigenständigen Schaltkreisentwurfsarbeiten waren umfangreiche materielle und personelle Voraussetzungen in der Anwenderindustrie zu schaffen. Die Qualifizierung der Kader erfolgte dabei durch aktive Unterstützung der Bauelementehersteller, zum Großteil wurden Kader zielgerichtet in den Entwurfsbereichen der Bauelementehersteller qualifiziert.

Heute ist festzustellen, daß im Bereich der Elektrotechnik/Elektronik alle Hauptanwender der Mikroelektronik leistungsfähige Entwurfsbereiche aufgebaut haben. Darüber hinaus sind auch in solchen Bereichen wie Textilmaschinenbau, Werkzeugmaschinenbau, Schwermaschinen- und Anlagenbau, Allgemeiner Maschinenbau und Metallurgie die Voraussetzungen zu eigenen Entwurfsleistungen für ASIC-Schaltkreise erfüllt. Damit bestehen in den Kombinaten und Betrieben der Volkswirtschaft außerhalb der Bauelementehersteller mehr als zehn arbeitsfähige Entwurfszentren. 1990 können mit diesen Kapazitäten 120 ... 150 ASIC-Entwürfe realisiert werden, die mindestens zu 70 ... 80 produktionswirksamen Bauelementelösungen führen werden. Ergänzt werden diese Kapazitäten durch eigenständige Entwurfsleistungen in den Einrichtungen der Akademie der Wissenschaften der DDR sowie den Universitäten und Hochschulen, die sowohl für die studentische Qualifizierung wie auch für Forschungsleistungen von großer Bedeutung sind. Die Anwendung der Mikroelektronik und der Einsatz von ASIC wird über die sich derzeitig profilierenden Kombinate und Industriebereiche hinausgehen。Deshalb kommt den bestehenden Entwurfszentren für die Qualifizierung, Verallgemeinerung von Erfahrungen und als Kooperationspartner eine besondere Bedeutung im Rahmen ihres Territoriums zu. Beispiel dafür ist das Schaltkreiszentrum im VEB Textimaelektronik Karl-Marx-Stadt, das vorrangig alle interessierten Anwender des Territoriums im Rahmen einer Nutzergemeinschaft zur Einführung und Anwendung von ASIC erfaßt hat. Damit wird das Schaltkreiszentrum wissenschaftlicher und technischer Kooperationspartner für einen breiten Anwenderbereich, der neben der Anwendungsberatung, auftragsbezogen die Realisierung von Entwurfsarbeiten übernimmt und sich künftig auch auf die Übernahme von arbeitsteiligen Fertigungsprozessen aus der Bauelementeindustrie vorbereitet.

Bild 2: Kooperationsbeziehungen zwischen Bauelementehersteller und -anwender bei der Entwicklung und Produktion von halbkundenspezifischen Schaltkreisen (am Beispiel von Gate-Arrays)

Da sich die Realisierung von kleinen Stückzahlen in speziellen Anwendungsgebieten auch gerade für Klein- und Mittelbetriebe anbietet, sind auch die Ingenieurbetriebe für die Anwendung der Mikroelektronik (IfAM) in den Beratungs- und Applikationsprozeß zur Anwendung von ASIC einbezogen. Die in allen Bezirken tätigen IfAM stehen in diesem Rahmen als Konsulationspartner für die ASIC-Anwendung zur Verfügung; für spezielle Applikationsunterstützung für Gate-Array-Schaltkreise hat sich der IfAM Dresden im VEB Forschungszentrum Mikroelektronik Dresden, Betrieb des Kombinates VEB Carl Zeiss Jena und für ISA-Schaltkreise der IfAM Frankfurt (Oder) profiliert.

#### 4. Erfahrungen bei der Zusammenarbeit von Bauelementeherstellern und -anwendern

Sowohl die potentiellen Anwender der Mikroelektronik wie auch neue Industriebereiche orientierten sich rechtzeitig auf den Einsatz von ASIC. So konnten bereits nach einem Jahr nach Produktionseinführung des Gate-Array- und Standardzellen-Systems in diesen Kombinaten und Betrieben eigene Entwurfs- und Applikationsleistungen erfolgreich realisiert werden.

Folgende Erfahrungen sind für Kombinate und Betriebe abzuleiten, die vor dem Einstieg in die Anwendung von ASIC stehen bzw. die einen breiteren und forcierten ASIC-Einsatz vorbereiten:

- Analysen des internationalen Standes des Einsatzes der Mikroelektronik, und insbesondere des Anteils von ASIC verbunden mit langfristigen Systemkonzepten für die Gerätelösungen sind Voraussetzung zur Profilierung konkreter ASIC-Anforderungen; die planwirksame Ausarbeitung von Studien zum langfristigen Mikroelektronik- und ASIC-Einsatz für den Erzeugnisvorlauf sollten somit wesentliche Voraussetzungen der ASIC-Anwendungsvorbereitung sein.

- Die Qualifizierung und Orientierung zum ASIC-Einsatz ist bei den H/F-Kadern in F/E-Bereichen der Geräteindustrie effektiver durchzusetzen; derzeitig wird der ASIC-Einsatz vorrangig und noch zu einseitig durch die Entwurfszentren getragen und nicht in Arbeitsteilung mit den Themenkollektiven beim Gerätehersteller. Ein Teil der Entwürfe und Prototypen werden nicht zur Produktionsreife geführt, da sie nicht zeitgleich mit den Geräteentwicklungen liegen. Es ist erforderlich, die Themenkollektive im Rahmen der Bearbeitung der Pflichtenhefte und Erzeugnispässe zum ASIC-Einsatz zu bewerten. Im Pflichtenheft/Erzeugnispaß sind Aussagen zum ASIC-Einsatz in vergleichbaren internationalen Erzeugnislinien zu treffen und die Zielstellung zur eigenen Entwicklung abzuleiten.

- Die Heranführung geeigneter Kader ist in den Entwicklungsbereichen der Geräteindustrie an arbeitsteilige Entwurfsschritte als Kooperationspartner für die Entwurfszentren weiterzuführen. Damit wird in den F/E-Kollektiven eine "Angstschwelle", die die aktive Mitarbeit und fachliche Forderung des Entwurfszentrums eingrenzt, abgebaut. Hier besteht die Aufgabe, die in den Entwurfszentren gesammelten Erfahrungen zielgerichtet für die Qualifizierung von Gerätentwicklern in den Finalbereichen zu nutzen. Das ist ein prinzipielles Erfordernis, da sich leistungsfähige Entwurfszentren als Kooperations- und Applikationspartner dienstleistungsbezogen anbieten, vom Finalproduzenten jedoch eine elektronisch aufbereitete Systemlösung und -logik erwartet wird.

- Die zielgerichtete Qualifizierung und Verallgemeinerung von Erfahrungen durch die Entwurfszentren muß immer mehr im Rahmen von Nutzergemeinschaften unter Leitung eines leistungsfähigen Entwurfszentrums erfolgen; diese Nutzergemeinschaften sollen sowohl die Breite der Kombinate und Betriebe des Industriebereichs erfassen, wie auch innerhalb des Territoriums künftige Anwender zum ASIC-Einsatz befähigen. Dies bedeutet sowohl die Heranführung von Erstanwendern wie auch die Schaffung effektiver Arbeits- und Kooperationsbeziehungen zwischen den beteiligten Entwurfszentren und potentiellen Nutzern. Damit nehmen die Nutzergemeinschaften unmittelbaren Einfluß auf die Anwendungsgeschwindigkeit von ASIC und sind eine entsprechende Organisationsform für die Realisierung der Leitfunktion der Entwurfszentren.

#### 5. Ükonomische Effekte beim Einsatz anwenderspezifischer Schaltkreise

Der ökonomische Nutzen des Einsatzes von ISA-Schaltkreisen, Gate-Arrays und Standardzellen-Schaltkreisen gegenüber Vollkunden-Schaltkreisen setzt sich aus mehreren Nutzenseffekten zusammen.

Direkt nachweisbare Effekte ergeben sich:

- bei der Entwicklung von ASIC durch Einsparung von Entwicklungsaufwendungen um mehr als 50 % und in der Verkürzung der Entwicklungszeit von ca. 2 Jahren auf 1/2 ... 3/4 Jahre

- bei der Anwendung von ASIC durch Einsparung von Grundmaterialien (insbesondere aktiven und passiven Bauelementen und Leiterplattenmaterial) und Arbeitszeiteinsparungen an Bestückungs-, Test- und Prüfzeiten.

Darüber hinaus treten folgende ökonomische Effekte auf, die sich in der Gesamtökonomie der Geräteentwicklung und der Geräteanwendung niederschlagen:

- Einsparung des Energiebedarfs um 30 ... 40 % durch Reduzierung des Bauelementeumfangs und Einsatzes der leistungsarmen CMOS-Technologie und damit Reduzierung des Aufwandes für die Stromversorgung und Kühlung

- Reduzierung der Geräteabmessungen (Volumen) und Einsparungen im mechanischen Aufwand

- bis zu 20 % h\u00f6here Zuverl\u00e4ssigkeit auf Grund der Reduzierung von L\u00f6tstellen, Kontaktbauelementen und des Gesamtumfangs von aktiven und passiven Bauelementen, damit verbunden ist die

Reduzierung des Wartungs-, Reparatur- und Serviceaufwandes.

#### 6. Weiterentwicklung anwenderspezifischer Schaltkreise in der DDR

Die konzipierten Anwendungen von ASIC sind nicht allein auf die traditionellen Bereiche der Elektrotechnik/Elektronik beschränkt sondern eröffnen insgesamt für die Volkswirtschaft der DDR folgende perspektivischen Anwendungsschwerpunkte:

- wissenschaftlich-technischer Gerätebau, technologische Spezialausrüstungen und Fototechnik

- Schreib-, Druck- und Speichertechnik, Rechen- und Meßtechnik

- Automatisierungsanlagen, Steuerungstechnik, spezielle Interface-Schaltkreise, Signal- und Sicherungstechnik, Elektroenergieanlagen, elektronische Schutztechnik, Medizintechnik

- Steuerungen für die Textilindustrie und für den Werkzeugmaschinenbau, Robotersteuerungen, Antriebstechnik, Automatisierungsbaugruppen der flexiblen Automatisierung

- digitale Vermittlungs- und Übertragungstechnik, Endgerätetechnik, Funktechnik

- digitale Signalverarbeitung in Hör- und Fernsehrundfunkempfängern, Satellitenempfangstechnik,

Tonspeichertechnik

- Sicherheitstechnik, Qualitätssicherungssysteme (Meßcomputer), Videotechnik, CCD-Technik,

Bordrechner für Einsatz in Fahrzeugen und für Militärtechnik

- Klimaschränke, Industrieöfen, Verseilmaschinen, Aufzüge, Gurtbandförderer, Werkzeugmaschinen,

Dieselmotore, Baumaschinen

Aufgrund der großen Breite o. a. Einsatzentwicklung werden sich die ASIC-Stückzahlen und das Sortiment – wie im Bild 3 dargestellt – in unserer Volkswirtschaft im Perspektivzeitraum planmäßig entwickeln. Dies bedeutet insgesamt eine Steigerung des Gesamtaufkommens um 266 % in den betrachteten Fünfjahrzeitraum.

Bild 3: Perspektivische Entwicklung des ASIC-Bedarfs in der DDR

Die Weiterentwicklung von ASIC-Grundstrukturen wird in der DDR wie folgt erfolgen:

- Ausbau und Verbesserung der vorhandenen Systeme durch Verfeinerung von Entwurf und Technologie,

Erhöhung des Integrationsgrades, Erweiterung der Zellenbibliothek und der Mastervarianten

(z. B. Funktionsblöcke, analoge Funktionen)

- Entwicklung von programmierbaren Logikschaltkreisen (PLD)

- Bereitstellung von ergänzenden Bauelementelinien aus dem RGW im Rahmen der sozialistischen ökonomischen Integration

#### 7. Zusammenfassung

Es kann eingeschätzt werden, daß mit den durch die Bauelementehersteller der DDR bereitgestellten ASIC-Lösungen eine moderne Ergänzung im Rahmen des Sortimentsangebots elektronischer Bauelemente bereitsteht.

Mit den drei ASIC-Technologievarianten ISA-Schaltkreise, Gate-Arrays und Standardzellen-Schaltkreise werden die überwiegenden Anforderungen abgedeckt und es kommt insbesondere darauf an, die wissenschaftlich-technischen Lösungsvarianten durch eine effektive Entwurfs- und Applikationsarbeit auszunutzen.

Hohe ökonomische Effekte sind bei den Beispielen des ASIC-Einsatzes in der Volkswirtschaft nachgewiesen. Die weitere Profilierung der installierten Entwurfszentren als Wissensvermittler und Kooperationspartner im Rahmen ihrer Kombinate, Industriebereiche und Territorien ist fortzuführen und ein breiter Kreis von Erstanwendern weiter an den ASIC-Einsatz heranzuführen. Dies schließt auch ein, daß die genannten Anwendungsprobleme schnell und wirksam überwunden werden. Unter dieser Zielstellung werden die gestellten Anforderungen zum erweiterten Einsatz von Schlüsseltechnologien wie der Mikroelektronik in breitesten Bereichen der Anwenderindustrie erfüllt werden können und es wird ein wirksamer Beitrag zur Erhöhung der Leistungsfähigkeit unserer Volkswirtschaft geleistet.

#### Literatur

- /1/ Auer, L.: Semi-Kundenschaltkreise in Forschung/Entwicklung und Technologie der Nachrichtentechnik INT-Mitt., Berlin 8 (1986)1, S. 3 ... 5

- /2/ Fischer, W.-J. u. a.: CMOS-Gate-Array System U 5200 Nachrichtentechnik Elektronik, Berlin 36 (1986)1, S. 21 ... 23

- /3/ Tüngler, V.; Warning, D.; Hamann, O.: Realisierung von nachrichtenspezifischen Schaltkreisen mit Hilfe von Halbkundentechniken der Bipolartechnologie

Nachrichtentechnik Elektronik, Berlin 36 (1986)1, S. 24 ... 26

- /4/ Buchelt, A.: Meßtechnik nachrichtenspezifischer Schaltkreise INT-Mitt., Berlin 8 (1986)4, S. 7 ... 12

- /5/ Knobloch, J.; Fischer, W.-J.: Mikroelektronische Chips maßgeschneidert: CMOS-Gate-Array-Schaltkreise Wiss. und Fortschritt, Berlin 36 (1986)4, S. 94 ... 97

- /6/ Schröter, K.; Pritzke, B.: Anwendungsspezifische integrierte Schaltung U 1504 D in Standardzellentechnik Radio Fernsehen Elektronik, Berlin 35 (1986)5, S. 280 ... 281

- /7/ Heidgen, F.: Entwicklung einer Zuverlässigkeitsprüfeinrichtung für nachrichtentechnische Kundenschaltkreise Nachrichtentechnik Elektronik, Berlin 36 (1986)10, S. 394 ... 396

- /8/ Sorst, M; Gieseler, M; Fischer, W.-J.: CMOS-Gate-Array-System U 5200 Mikroprozessortechnik, Berlin 1 (1987)1, S. 4 ... 8

- /9/ Groß, W.: ISACAD-Entwurfssystem für Gate-Array-Schaltkreise Mikroprozessortechnik, Berlin 1 (1987)4, S. 104 ... 108

- /10/ Biebler, K.: Allgemeine Tendenzen in der Entwicklung neuer mikroelektronischer Bauelemente Nachrichtentechnik Elektronik, Berlin 37 (1987)4, S. 122 ... 129

- /11/ Lehmann, K.: Koppehel, W.-G.: Test applikationsspezifischer digitaler Schaltkreise Nachrichtentechnik Elektronik, Berlin 37 (1987)8, S. 301 ... 302

- /12/ Samsonov, N. S.: Sowjetisches Gate-Array K 1520 XM 2 Radio Fernsehen Elektronik, Berlin 36 (1987)11, S. 695 ... 696

Dipl.-Ing. Gerhard Neugebauer

VEB Halbleiterwerk Frankfurt/Oder im VEB Kombinat Mikroelektronik

# Integrierte Schaltungsanordnungen aus dem VEB Halbleiterwerk Frankfurt/Oder

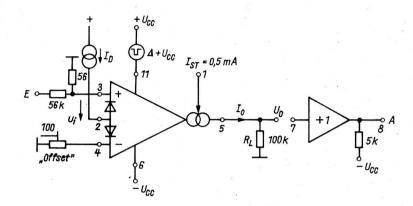

Es wird ein Entwurfssystem für anwenderspezifische Schaltkreise erläutert. Der zukünftige Anwender gestaltet selbst den Entwurf seines integrierten Schalt-kreises (IS) und die spezifische Meßtechnik. Der Bauelementehersteller bietet ihm als IS-Entwurfshilfen Verfahren des rechnergestützten Entwurfs (ISACAD).

#### 1. Ziele

International hat die Herstellung und Anwendung von anwenderspezifischen Schaltkreisen in den letzten Jahren überdurchschnittlich an Bedeutung gewonnen. Diesem Trend entsprechend wurde vom VEB Halbleiterwerk Frankfurt/Oder (HWF) ein neues Array-System entwickelt, das den Entwurf und die Realisierung von anwenderspezifischen Schaltkreisen zum Ziel hat. Die Systembezeichnung "ISA" steht für integrierte Schaltungsanordnungen.

Die mehrjährigen Kundenerfahrungen des VEB HWF mit dem System IA 10 bis IA 60 und ID 10 bis ID 30 ordnen sich auf Grund der erzielbaren Effekte in die verstärkten internationalen Erkenntnisse zur Entwicklung anwenderspezifischer Schaltkreise ein. Der Einsatz von anwenderspezifischen Schaltkreisen trägt in hohem Maße zur Strukturveränderung in allen Zweigen der Geräteindustrie bei.

Wesentliche Merkmale dieser Entwicklung sind:

- Schaffung völlig neuer Generationen von Gerätesystemen durch Nutzung der Vorteile der Mikroelektronik, wie höhere Schaltungskomplexität, geringere Verarbeitungszeiten, geringere Leistungsaufnahme, höhere Zuverlässigkeit

- Einsparung von Material und Verarbeitungsenergie in der Anwenderindustrie

- Erschließung des Systementwurfspotentials der Anwenderindustrie für die breite und direkte Nutzung der Mikroelektronik.

#### Systemkonzept

Anwenderspezifische Schaltkreise sind ein weiterer Schritt zu einfacheren Herstellungs- und Entwicklungsverfahren von IS. Im Gegensatz zu einem Vollkunden-Schaltkreis, bei dem alle Prozeßschritte auf das Einzelprodukt abgestimmt sind, wird bei einem ISA-Schaltkreis die vom Bauelementehersteller vorgegebene Chip-Bauteilestruktur (d. h. einzelne Transistoren, Gatter, Widerstände und Kapazitäten) nach Anwenderspezifikation über die Metallisierungsebene verdrahtet.

Anwenderspezifische Schaltkreise werden somit nur in den letzten Fertigungsschritten anwenderspezifisch gestaltet und die Bezeichnung ISA-Schaltkreise bezieht sich somit nur auf den Fertigungsablauf, das Endprodukt jedoch ist ein vollwertiger IS.

Durch dieses Verfahrensprinzip werden folgende Vorteile wirksam:

- Reduzierung der Entwicklungszeit für den speziellen Schaltkreis durch den ständigen Zugriff auf vorgefertigte Scheiben mit der vom Bauelementehersteller vorgegebenen Chip-Bauteilestruktur

- Verringerung des Risikos der IS-Entwicklung, da die Entwicklung der ISA-Arrays durch den Bauelementehersteller zu Beginn der Entwicklung eines anwenderspezifischen Schaltkreises bereits abgeschlossen ist, die Herstellungstechnologie reproduzierbar beherrscht wird und ähnlich wie bei Standardschaltkreisen abläuft.

Um die verschiedenen Anwenderforderungen rationell und schnell zu lösen, ist es notwendig, in derartigen Systemen mehrere Arrays, im weiteren als Grundchip bezeichnet, zur Verfügung zu haben.

Das HWF-ISA-System bietet diese Grundchips in verschiedener Größe, Einzelstrukturanordnung und Grundtechnologie an. Bei der Konstruktion eines ISA-Schaltkreises wird vom Anwender somit derjenige Chip ausgewählt, der seinen spezifischen Anforderungen am besten genügt und ein Leitbahnmuster entworfen, das die auf dem Chip angeordneten Einzelstrukturen gemäß der geforderten elektrischen Funktionen verbindet. Nicht benutzte Einzelstrukturen bleiben unbeschaltet. Da alle Einzelstrukturen frei zugänglich sind, gibt es eine sehr große Anzahl von Möglichkeiten, die auf den Grundchips angeordneten Einzelstrukturen durch ein entsprechendes Leitbahnmuster zu verbinden.

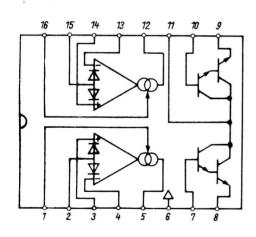

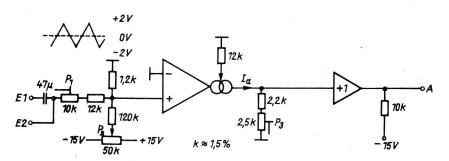

#### 3. ISA-Grundchips

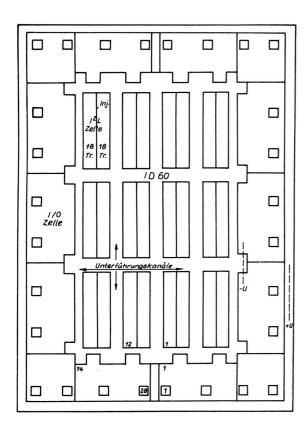

Für den ISACAD-Entwurf stehen vier bipolare Grundchips ID 40, ID 50, ID 60 und ID 70 zur Verfügung. Dic Grundchips zeichnen sich durch identischen Aufbau, einheitlichen Verdrahtungsraster und Bibliothekfähigkeit aus. Die Grundchips sind für Betriebsspannungen bis 20 V und für das im HWF verfügbare Gehäusesortiment zugelassen (Tabellen 1 und 2). Der prinzipielle Aufbau der Grundchips ist am Beispiel ID 60 erläutert.

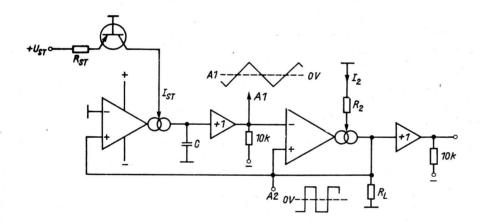

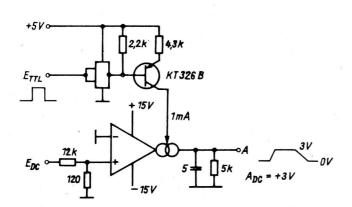

Auf dem ID 60 sind enthalten (Bild 1):

- 12  ${ iny 1}^2$ L-Transistorzellen, die durch Injektoren in 24 Halbzellen mit je 18 Transistoren getrennt werden

- 14 Interfacezellen mit je zwei Bondinseln und ca. 10 Transistoren.

Die Verbindung zwischen den I<sup>2</sup>L-Zellen erfolgt an Kreuzungspunkten über niederohmige Unterführungskanäle. Die Konstruktionspunkte der Kontakt- und Leitbahnebene liegen in einem vorgegebenen Raster. Mit dieser Maßgabe werden weitgehend gerade Leitbahnführungen in allen Chipteilen möglich.

#### 4. ISACAD

Das Programmsystem ISACAD dient der Entwicklung digitaler und analoger ISA-Schaltkreise.

Mit dem Einsatz des ISACAD bei ISA-Schaltkreisentwicklungen erhält jeder Kunde datenmäßig die Unterstützung, die er je nach Erfahrungs- und Kenntnisstand für seine spezielle Schaltkreisentwicklung benötigt. Die Entwurfssoftware ISACAD ermöglicht es für die Grundchips ID 40 bis 70, die Verdrahtungsebenen weitgehend automatisch von der Schaltung bis zum Layout zu entwerfen. Die mit ISACAD angebotene Entwurfshilfe betrifft den Schaltungsentwurf, die Schaltungssimulation, die automatische Verdrahtung der Grundchips gemäß Schaltungsvorlage, die Kontrolldurchläufe zur Einhaltung der Entwurfsvorgaben von ISA-Schaltkreisen und natürlich die vollständige Erstellung der Steuerdaten zur Maskenherstellung.

Bild 1: Prinzipieller Aufbau des Grundchips ID 60 aus dem ISA-System

Die Schritte, die der Anwender mit dem Programmsystem ISACAD durchführen muß, um von der Schaltung zum Layout zu gelangen, sind

- . Schaltungseingabe

- . Schaltungssimulation und

- . Symbollayouterzeugung.

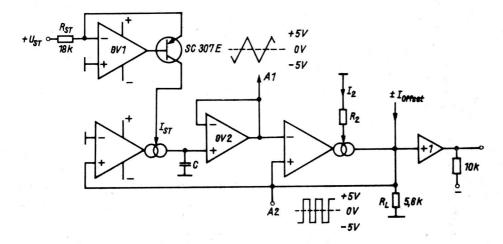

#### 5. Entwicklungsablauf

Die Entwicklung von ISA-Schaltkreisen erfolgt in zwei Etappen. Die erste Etappe dient der Layout-findung und endet mit der Herstellung funktionstüchtiger Muster. In einer zweiten Etappe, der Überleitungsetappe, erfolgt die Produktionseinführung des neuen IS-Erzeugnisses, um die Voraussetzungen für eine bedarfs- und qualitätsgerechte Herstellung zu schaffen.

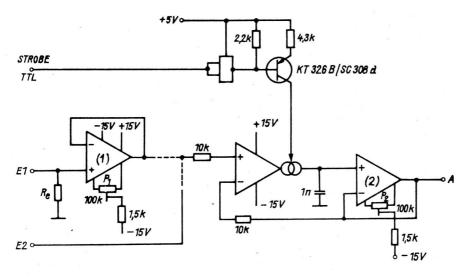

Die Schnittstellen zwischen Anwender und Bauelementehersteller in der ersten Etappe resultieren aus der arbeitsteiligen Aufgabenstellung und sind in Bild 2 zusammenfassend schematisiert.

Bild 2: Schnittstellen zwischen Anwender und Bauelementehersteller aufgrund der arbeitsteiligen Aufgabenstellung in der ersten Etappe der Entwicklung von ISA-Schaltkreisen

Die Realisierung von ISA-Schaltkreisen erfordert eine neue Form der Arbeitsteilung zwischen Anwender und Bauelementehersteller. Das Problem, das der Anwender und Bauelementehersteller zu lösen haben, besteht darin, das Gerätekonzept mit der Technologie der Anwender-Bausteine in Einklang zu bringen, also für den unverdrahteten Chip die richtige Verdrahtung im Sinne der Anwendung zu finden. Der ISA-Anwender hat eigenverantwortlich und in Abstimmung mit dem Bauelementehersteller

- . den IS-Entwurf (Schaltung, Layout, Gehäuse)

- . und den IS-Meßtechnik-Bau

durchzuführen. Dabei kann er Kooperationsleistungen für Schaltungs-, Meßtechnik- und Layoutentwurf der vorhandenen Entwurfszentren in Anspruch nehmen.

Tabelle 1: Bipolare Grundchips ID 40 bis ID 70 für ISACAD-Entwurf

| Grundchip        |                     | ID 40   | ID 50   | ID 60   | ID 70   |

|------------------|---------------------|---------|---------|---------|---------|

| Betriebsspannung | g in V              | max. 20 | max. 20 | max. 20 | max. 20 |

| Einsatzgebiete:  | digital             | ×       |         | ×       | *.      |

|                  | linear/digi-<br>tal | ¥       | х       |         | x       |

| Bondinseln       |                     | 40      | 40      | 28      | 40      |

### Fortsetzung Tabelle 1

| Grundchip                   | ID 40 | ID 50 | ID 60 | ID <b>7</b> 0 |

|-----------------------------|-------|-------|-------|---------------|

| Gehäuse: DIP 18             | _     | -     | ×     | _             |

| DIP 28                      | ×     | ×     | ×     | x             |

| DIP 40                      | ×     | ×     | _     | ×             |

| QFP 48                      | ×     | ×     | -     | ×             |

| I <sup>2</sup> L-Gatter     | 864   | 216   | 432   | 432           |

| (je 4 Ausgänge)             |       |       |       |               |

| npn-Transistoren            | 170   | 303   | 120   | 231           |

| pnp-Transistoren            | 38    | 129   | 34    | 91            |

| Transistoren insqesamt      | 208   | 432   | 154   | 322           |

| Gesamtwiderstand<br>in MOhm | 1,732 | 1,886 | 1,292 | 1,610         |

| Gesamtkapazität<br>in pF    |       | 62    | -     | 44            |

Tabelle 2: Elektrische Eigenschaften der 20-V- $\mathrm{I}^2\mathrm{L}$ -Grundchips ID 40 bis ID 70

10<sup>-3</sup> ... 50 <sup>1</sup>)

### npn-Transistoren

Arbeitsbereich  $\mathbf{I}_{\mathsf{C}}$  in  $\mathsf{m}\mathsf{A}$

| U <sub>C</sub> in V                 |          | ca. 1 20             |

|-------------------------------------|----------|----------------------|

| Stromverstärkung h <sub>21E</sub>   |          | 50 200               |

| Grenzfrequenz f <sub>T</sub> in MHz | <b>\</b> | 300                  |

|                                     |          |                      |

| pnp-Transistoren                    | ē        |                      |

| Arbeitsbereich I <sub>C</sub> in mA |          | 10 <sup>-4</sup> 0,5 |

| $^{ m U}_{ m C}$ in V               |          | 1 20                 |

| Stromverstärkung h <sub>21E</sub>   |          | 5 50                 |

| Grenzfrequenz f <sub>T</sub> in MHz |          | 5                    |

Anm.: 1) je nach npn-Typ

Fortsetzung Tabelle 2

## I<sup>2</sup>L-Transistoren

Arbeitsbereich  $I_{inj}$  in /uA 0,1 ... 100

$U_{\mathrm{BR}}$  in V 2,5

Stromverstärkung B<sub>eff</sub> 2,5

Taktfrequenz

(D-FF bei 100 /uA) in MHz

Widerstände

Nominalwerte in kOhm 0,5; 1; 2,5; 0,1 ... 1 variabel

10; 20

Oxidkapazitäten

Nominalwerte in pF 1,5; 3; 6

Dr.-Ing., Dr. oec. Werner Jöstel Dipl.-Ing. ök. Ina Suchant

TU Dresden, Sektion Sozialistische Betriebswirtschaft WB Betriebsplanung/-abrechnung/-analyse

# Anwenderspezifische Schaltkreise -Methoden zur ökonomischen Bewertung

#### O. Einleitung

Die Realisierung der vom XI. Parteitag beschlossenen ökonomischen Strategie basiert auf einer breiten Anwendung der Schlüsseltechnologien in allen Bereichen der Volkswirtschaft. Dieser Prozeß ist durch die Entwicklung mikroelektronischer Bauelemente, die die Ökonomie von Entwickler, Bauelementehersteller und Anwender vereinen, nachhaltig zu beschleunigen.

In diesem Zusammenhang erlangen anwenderspezifische Schaltkreise zunehmende Bedeutung. In der Direktive zum Volkswirtschaftsplan der DDR für die Jahre 1986 bis 1990 ist deshalb die Aufgabe gestellt, die Entwicklung und Produktion von anwenderspezifischen Schaltkreisen zu verstärken und dazu mikroelektronische Produktionskapazitäten in den Kombinaten der verarbeitenden Industrie aufzubauen /1/.

Aufgrund der unterschiedlichen Realisierungsmöglichkeiten von anwenderspezifischen Schaltkreisen ist für jeden komplexen Anwendungsfall die Zusammenarbeit von Technikern und Ökonomen erforderlich. Ökonomische Bewertungsmethoden können dabei den Prozeß der Einsatzvorbereitung wesentlich unterstützen.

#### 1. Anwenderspezifische Schaltkreise

Für die Vollkunden-Schaltkreise ist charakteristisch, daß alle Prozeßschritte auf das Endprodukt abgestimmt sind, vom Schaltkreisentwurf bis zum fertig getesteten Schaltkreis. Der Aufbau, die Auswahl und die Anordnung der einzelnen Funktionsgruppen auf dem Chip erfolgt entsprechend den individuellen Wünschen des Kunden.

Standardzellen-Schaltkreise bestehen aus fertig entwickelten logischen Grundelementen. Auf der Grundlage der vom Bauelementehersteller vorgegebenen Funktionsgruppen stellt der Anwender den Entwurf selbst her. Die Erstellung aller notwendigen Masken für die Schaltkreisstrukturierung erfolgt anwenderspezifisch.

Gate-Arrays besitzen vorgefertigte Masterchips mit hochgradig regelmäßigen Belegungen durch logische Elementargatter oder verwandte Vorstrukturen. Die individuellen Kundenfunktionen werden simuliert und nachfolgend dazugehörige Verdrahtungsmuster gefertigt.

### 2. Ükonomische Bewertungsmethoden für anwenderspezifische Schaltkreise

Das Ziel der ökonomischen Bewertung von Vollkunden- und Standardzellen-Schaltkreisen sowie von Gate-Arrays besteht im Erkennen der effektivsten Entwicklungs- und Produktionsvariante für einen vorgegebenen Anwendungsfall. Für die Durchführung der ökonomischen Bewertung im Entscheidungsprozeß stehen vielfältige Methoden zur Verfügung. Der Auswahl geeigneter Bewertungsmethoden sollten

folgende Prämissen zugrunde gelegt werden:

- Einbeziehung aussagekräftiger ökonomischer Bewertungskriterien

- Kompensation technischer und technologischer Unterschiede der anwenderspezifischen Schaltkreise

- Verbindung der Bewertungskriterien unter Berücksichtigung der Betrachtungsebenen

Volkswirtschaft Bauelementehersteller Anwender.

Unter Berücksichtigung dieser Kriterien kommen für die ökonomische Bewertung anwenderspezifischer Schaltkreise folgende Methoden in Betracht:

- 1. Ukonomischer Objektvergleich

- 2. Gebrauchswert-Kosten-Analyse

- 3. Ermittlung der Rentabilitätsschwelle

- 4. Technologischer Variantenvergleich

- 5. Methodischer Zielbaum

#### 2.1. Ökonomischer Objektvergleich

Grundlage für einen ökonomischen Objektvergleich bilden Aufwands-, Ergebnis- und Effektivitätskennziffern.

Vergleiche sind möglich bezüglich:

- einer Basisvariante (Standardschaltkreise),

- dem wissenschaftlich-technischen Höchststand,

- der Zielstellung.

Die Wahl der Vergleichsbasis und die Vergleichbarkeit der Kennziffern spielen eine sehr wichtige Rolle bei der Anwendung dieser Methode. Darüber hinaus muß auf der Grundlage eines einheitlichen Maßstabes die Gegenüberstellung inhaltlich und ökonomisch sinnvoll sein.

Aufgrund dieser Tatsache, daß die anwenderspezifischen Schaltkreise technische und technologische Unterschiede aufweisen (s. Tabelle 1), führt der globale Vergleich von Kennziffern zu unsicheren Bewertungen, da die Kompensation der genannten Unterschiede praktisch schwer realisierbar ist.

Tabelle 1: Gegenüberstellung technischer und technologischer Daten anwenderspezifischer Schaltkreise

| IS-Typ                                            | Techno-<br>logie | Niveau | Chipgröße<br>in<br>mm x mm | Scheiben-<br>durchmesser<br>in mm | Gehäuse | Chips/<br>Scheibe | Ebenen |

|---------------------------------------------------|------------------|--------|----------------------------|-----------------------------------|---------|-------------------|--------|

| U 115 I<br>(Vollkunden-<br>Schaltkreis)           | CSGT 1           | Ι      | 2,90 x 3,30                | 76                                | Keramik | 367               | 10     |

| V 1506 C<br>(Standard-<br>zellen-<br>Schaltkreis) | CSGT 2           | II     | 4,00 x 5,00                | 100                               | Plast   | 268               | 10     |

| U 5201 RC                                         | CSGT 2           | II     | 7,04 x 7,46                | 100                               | Keramik | 100               | 12     |

| (Gate-Array)                                      |                  |        |                            |                                   |         |                   |        |

#### 2.2. Gebrauchswert-Kosten-Analyse

Ausgangspunkt für die Durchführung der Gebrauchswert-Kosten-Analyse (GKA) sind gebrauchswertmäßige Vorgaben für die neuen Schaltkreis-Typen, die in entsprechenden technischen und ökonomischen

Kennziffern ausgedrückt werden. Das Ziel der Analyse besteht in dem Finden der Variante mit dem

günstigsten Verhältnis von Gebrauchswert und Kosten mit Hilfe des Gebrauchswert-Kosten-Index

und des direkten Vergleichs /2/.

Gebrauchswertindex (G) =

$$\frac{G_{\text{neu}}}{G_{\text{alt}}}$$

(1)

Kostenindex (Ko)

$$= \frac{Ko_{alt}}{Ko_{neu}}$$

(2)

Gebrauchswert-Kosten-Index (GK) =

$$\frac{G_{neu}}{G_{alt}} \times \frac{Ko_{alt}}{Ko_{neu}}$$

(3)

direkter Vergleich:

$$\frac{G_{alt}}{Ko_{alt}} < \frac{G_{neu}}{Ko_{neu}}$$

(4)

Die Anwendungsmöglichkeit dieser Methode für eine ökonomische Bewertung anwenderspezifischer Schaltkreise ist durch die auftretenden Probleme bei der exakten Erfassung der Abhängigkeiten zwischen Funktionen, Parametern und dem entsprechenden Kostenvolumen begrenzt. Als Basisvarianten können die Standardschaltkreise bzw. die jeweiligen anwenderspezifischen IS-Lösungen fungieren.

Nachteilig bei dieser Methode ist, daß für eine komplexe Bewertung anwenderspezifischer Lösungen die einbezogenen Kriterien Gebrauchswert und Kosten nicht ausreichen.

#### 2.3. Berechnung der Rentabilitätsschwelle

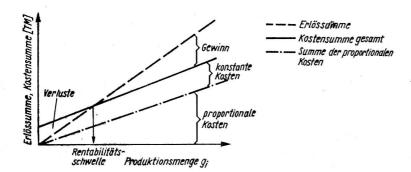

Die Ermittlung der Rentabilitätsschwelle (Rs) dient der Darstellung des Schnittpunktes zwischen der Kostenkurve und der Produktions- bzw. Erlöskurve. Bei Unterstellung einer konstanten Kapazität (Produktionsanlagen, Produktionsarbeiter) erhöht sich ab diesem Schnittpunkt der Gewinn bei zunehmender Leistungsmenge.

Das Grundprinzip besteht darin, zu ermitteln, welches Leistungsvolumen für die Deckung der konstanten Kosten und für die Gewinnerwirtschaftung erforderlich ist.

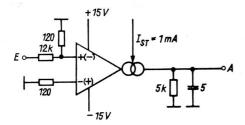

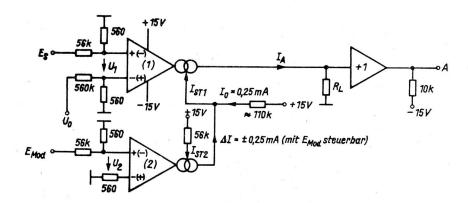

Grundlegende Voraussetzung für die Ermittlung von Rs ist die Erfassung der leistungsproportionalen Kosten (Grundmaterial, Stücklohnkosten u. a.) und der leistungsabhängigen konstanten Kosten (Abschreibungen, Zeitlöhne u. a.). Bild 1 zeigt den Zusammenhang zwischen Kosten und Gewinn zur Darstellung von Rs.

Bild 1: Darstellung der Rentabilitätsschwelle

Aufgrund des komplizierten Herstellungsprozesses von mikroelektronischen Bauelementen ist die exakte Kostenerfassung und die direkte bzw. indirekte Kostenverrechnung auf die entsprechenden Erzeugnisse sehr aufwendig, liefert jedoch dem Bauelementehersteller wichtige Informationen über die Effektivität des Entwicklungs- und Fertigungsprozesses anwenderspezifischer Schaltkreise.

#### 2.4. Technologischer Variantenvergleich

Der technologische Variantenvergleich ist eine Methode, mit der aus mehreren im Betrieb vorhandenen technologischen Varianten bei einer festgelegten Produktionsmenge die Variante mit dem Kostenminimum ausgewählt wird. Der technologische Variantenvergleich stellt einen Teilkostenvergleich dar, da nur die durch den technologischen Prozeß beeinflußten Kosten einbezogen sind. Es gibt zwei Methoden des technologischen Variantenvergleiches:

- a) Ermittlung der Grenzstückzahl und

- b) Ermittlung der Grenzlosanzahl.

Aufgrund der Losfertigung im Zyklus I bei der Herstellung mikroelektronischer Bauelemente empfiehlt sich die Methode der Grenzlosanzahl. Sie liefert für den Hersteller anwenderspezifischer Schaltkreise wesentliche Aussagen zu ökonomischen Stückzahlbereichen und Losgrößen.

Der methodische Ansatz geht von einer Aufteilung der technologischen Kosten in los- und stückzahlabhängige Kosten aus:

Die Grenzlosanzahl (LG), d. h. die Losgröße bei der entsprechend Gl. (5) Kostengleichheit zwischen einer Basisvariante (I) und einer alternativen Lösung (II) besteht, trennt die Wirtschaftlichkeitsbereiche zwischen den Varianten I und II.

Entsprechend Gl. (5) berechnet sich LG aus der Beziehung:

ks-stückabhängige Kosten in M/Stück

$$LG = \frac{ks \text{ II } - ks \text{ I}}{kl \text{ I } - kl \text{ II}} \times Q \tag{6}$$

Als Basisvarianten können sowohl Standardschaltkreise als auch die jeweiligen Typen anwenderspezifischer Schaltkreise angewendet werden.

Die Durchführung des technologischen Variantenvergleiches setzt aber, ebenso wie bei der Berechnung der Rentabilitätsschwelle, eine exakte Erfassung und Verrechnung der einzubeziehenden Kostenbestandteile voraus.

#### 2.5. Methodischer Zielbaum

Gegenüber den bisher betrachteten eingegrenzten Bewertungsmethoden zeichnet sich der methodische Zielbaum durch eine größere Komplexität, wie sie für anwenderspezifische Schaltkreise unbedingt erforderlich ist, aus.

Die wesentlichen Vorteile dieser Methode bestehen darin, daß Bewertungskriterien der Betrachtungsebenen Volkswirtschaft - Bauelementehersteller - Anwender integriert sowie technologische Unterschiede der Varianten durch entsprechende Bewertung kompensierbar sind. Da die Wichtung und Bewertung subjektive Momente beinhalten, ist eine Eingrenzung durch umfangreiche Expertenbefragungen

in den bauelementeherstellenden und Anwenderbetrieben unerläßlich. Für die Anwendung der Zielbaummethode ist das Festlegen von Haupt- und Nebenkriterien, deren Wichtung und eine Bewertung

der Varianten (Gate-Arrays, Vollkunden- und Standardzellen-Schaltkreise) notwendig.

#### 2.6. Kriterien und Bewertung

Bei der Auswahl von Bewertungskriterien sind grundsätzlich die Ebenen Volkswirtschaft - Bauelementehersteller - Anwender zu berücksichtigen. Es kann davon ausgegangen werden, daß eine

volkswirtschaftlich günstige Lösung für den Bauelementehersteller und auch für den Anwender ökonomisch vorteilhaft sein muß.

Unter diesem Gesichtspunkt sind z. B.:

- Stückzahl der Schaltkreise

- Gesamtselbstkosten

- Entwicklungszeit

- ökonomischer Anwendernutzen

- Effektivitätskriterien

- Zuverlässigkeit der Schaltkreis-Typen

wichtige Kriterien für die ökonomische Bewertung anwenderspezifischer Schaltkreise. Das Kriterium "Produktionsvolumen" ist insbesondere für den Bauelementehersteller von Interesse. Er ist bestrebt, mit dem jeweiligen Entwicklungsaufwand einen hohen Produktionsausstoß der spezifischen IS-Lösungen zu realisieren. Ein hohes Produktionsvolumen führt bei den Bauelementeherstellern zu:

- einem geringeren Aufwand für Umrüstungen der technischen Anlagen

- einer Senkung des Arbeitszeitaufwandes für die einzelnen Prozeßschritte in der Fertigung durch die fast routinemäßige Tätigkeit der Werktätigen

- einer effektiveren Auslastung der modernen Grundmittel

- einer bedeutenden Verringerung des organisatorischen Aufwandes.

Letztendlich richtet sich jedoch das Produktionsvolumen nach dem Bedarf der Kunden. Aus diesem Grund ist es wichtig zu ermitteln, in welchem Stückzahlbereich die Entwicklung der spezifischen IS-Lösungen ökonomisch vertretbar ist (z. B. mit Hilfe der Methode zur Ermittlung der Grenzlosanzahl).

Die Herstellungskosten lassen sich aus der folgenden Beziehung berechnen /3/:

$$Kic = KI + KM + KII + \frac{KE}{S} + \frac{KL}{S_{ges}}$$

(7)

Kic - Kosten für Herstellung eines Schaltkreises

KM - Siliziumkosten

KI - Kosten Scheibenprozeß

KII - Montage- und Endmeßkosten

KE - Entwurfskosten (Bauelementehersteller und Anwender)

S - Anzahl Schaltkreise eines Typs

KL - Entwurfskosten einer Basistechnologie

S<sub>ges</sub> - Anzahl aller mit der betreffenden Basistechnologie hergestellten Schaltkreise

Dabei sind bei der ökonomischen Bewertung besonders die beträchtlichen Niveauunterschiede in den Entwicklungs- und Schablonenkosten zwischen Gate-Arrays, Vollkunden- und Standardzellen-Schalt-kreisen zu beachten.

Eine tendenzielle Aussage zu ökonomischen Einsatzbereichen von anwenderspezifischen Schaltkreisen in Abhängigkeit von der Komplexität der Anwenderlösungen zeigt Bild 2.

Bild 2: Komplexitäts-/Stückzahlverhalten von anwenderspezifischen IS-Lösungen /4/

Die Entwicklungszeiten für die Erarbeitung des Entwurfes und der Erprobung stellen sowohl für den Bauelementehersteller als auch für den Anwender wichtige Bewertungskriterien dar. Kürzere Entwicklungszeiten für Gate-Arrays gegenüber den Standardzellen-Schaltkreisen resultieren aus der Vorfertigung des Grundmasters und der geringen Anzahl anwenderspezifischer Ebenen. Für Vollkunden-Schaltkreise ist die längste Entwicklungszeit zu verzeichnen.

Eine Einschätzung des ökonomischen Anwendernutzens kann primär durch die Substitution einer entsprechenden Anzahl von herkömmlichen Bauelementen, die für eine alternative Realisierung der Aufgabenstellung erforderlich sind, erfolgen. Eine differenzierte Bewertung des Anwendernutzens ist anhand folgender Kennziffern vorzunehmen:

- 1. Einsparung an Material

- . Standardschaltkreise

- . Leiterplatten

- . Lötzinn

- . Steckverbinder

- . weitere Materialien

- 2. Arbeitszeiteinsparung in der Fertigung des Finalerzeugnisses

- . Verkürzung der Montagezeit bei den Leiterplatten

- . Einsparung von Produktionskapazitäten arbeitskräfte- und anlagenbezogen

- 3. Entwicklung der Reparaturen der Finalerzeugnisse

- . Arbeitszeiteinsparung bei der Fehlersuche und Reparatur

- 4. Verbesserung der Gebrauchseigenschaften

- Erhöhung der Zuverlässigkeit des Finalerzeugnisses

- Volumenreduzierung und Senkung des Energiebedarfes bei den Finalerzeugnissen

- 5. Vergleich einer Lösung mittels Standard- und anwenderspezifischer Schaltkreise in bezug auf:

- . Forschungs- und Entwicklungsaufwand

- . Entwicklungszeit.

Der Ausweis der ökonomischen Effektivität ist vor allem für den Hersteller anwenderspezifischer Schaltkreise ein wichtiges Kriterium für die Wirtschaftlichkeit. Als wesentliche Kennziffern sind die kostenbezogene Rentabilitätsrate (kRT) und die Arbeitsproduktivität (Ap) der Bewertung zugrunde zu legen.

Die kostenbezogene Rentabilitätsrate (kRT) drückt die Effektivität des laufenden Aufwandes aus. Ihre Berechnung erfolgt nach der Beziehung:

Die Berechnung des Niveaus der Arbeitsproduktivität (Ap) für Gate-Arrays, Standardzellen- und Vollkunden-Schaltkreise kann mit Hilfe der Preissummenmethode erfolgen:

$$Ap = \frac{Q_i \times P_i}{T}$$

(10)

$\mathbf{Q}_{\mathbf{i}}$  – Produktionsmenge in Stück der einzelnen Erzeugnisarten i

P, - konstanter Planpreis der einzelnen Erzeugnisarten i

T - Aufwand an lebendiger Arbeit

Als Aufwandsgröße T ist der benötigte Arbeitszeitaufwand für die Herstellung der einzelnen anwenderspezifischen Schaltkreise anzusetzen. Er umfaßt den Aufwand für den Zyklus I, Zyklus II und die Meßtechnik. Dabei ist eine einheitliche Basisgröße (z.B. 1 000 gute Chips oder 1 000 Bauelemente) zu verwenden. Auf der Grundlage der genannten Kriterien ist mit Hilfe des methodischen Zielbaumes eine relativ komplexe Bewertung anwenderspezifischer Schaltkreise möglich. Die festzulegenden Haupt- und Neben-kriterien können zum Teil mit Hilfe der Methoden zur Berechnung der Grenzstückzahl, Grenzlosanzahl, Rentabilitätsschwelle und der Gebrauchswert-Kosten-Analyse ermittelt werden und objektivieren als wichtige Bewertungsbasen die Einschätzung der Gate-Arrays, Standardzellen- und Vollkunden-Schaltkreise.

In Tabelle 2 ist ein Zielbaum für die Bewertung der anwenderspezifischen Lösungen als Beispiel dargestellt, wobei die verwendeten Wichtungs- und Bewertungsfaktoren Schätzwerten entsprechen.

Tabelle 2: Methodischer Zielbaum für die ökonomische Bewertung anwenderspezifischer Lösungen

|                                  | Wich-                                 |               | Wich-<br>tung |                | Bewertung <sup>1</sup>                    |                             |  |

|----------------------------------|---------------------------------------|---------------|---------------|----------------|-------------------------------------------|-----------------------------|--|

|                                  | tung                                  |               |               | Gate-<br>Array | Standard-<br>zellen-<br>Schalt-<br>kreise | Vollkunden-<br>Schaltkreise |  |

|                                  | · · · · · · · · · · · · · · · · · · · |               |               |                |                                           |                             |  |

| Produktions-                     | 0,22                                  | _             | -             | 4              | 4                                         | 2                           |  |

| volumen                          |                                       |               |               | 0,88           | 0,88                                      | 0,44                        |  |

| Herstel-                         | 0,28                                  | Entwicklungs- | 0,3           | 3              | 4                                         | 1                           |  |

| lungs-<br>und Ent-<br>wicklungs- |                                       | kosten        |               | 0,25           | 0,34                                      | 0,08                        |  |

| kosten                           |                                       | Schablonen-   | 0,4           | 4              | 3                                         | 2                           |  |

|                                  |                                       | kosten        |               | 0,45           | 0,34                                      | 0,22                        |  |

|                                  |                                       | Grundlohn-    | 0,3           | 4              | 4                                         | 3                           |  |

|                                  |                                       | kosten        |               | 0,34           | 0,34                                      | 0,25                        |  |

| Entwick-                         | 0,17                                  | Präparation   | 0,6           | 5              | 3                                         | 2                           |  |

| lungs <b>-</b><br>z <b>eit</b>   | \$                                    |               |               | 0,51           | 0,30                                      | 0,20                        |  |

|                                  |                                       | Meßtechnik    | 0,4           | 5              | 3                                         | 2                           |  |

|                                  |                                       | . 1           |               | 0,34           | 0,20                                      | 0,14                        |  |

| Effek-                           | 0,18                                  | Ap            | 0,6           | 4              | 4                                         | 2                           |  |

| tivität                          |                                       |               |               | 0,43           | 0,43                                      | 0,21                        |  |

|                                  |                                       | kRT           | 0,4           | 3              | 4                                         | 3                           |  |

|                                  |                                       |               |               | 0,22           | 0,29                                      | 0,22                        |  |

| Zuver-                           | 0,15                                  | · <u>-</u>    | _             | 3              | 3                                         | 4                           |  |

| lässig-<br>keit                  |                                       |               |               | 0,45           | 0,45                                      | 0,60                        |  |

| Summe                            | 1                                     |               |               | 3,87           | 3,57                                      | 2,36                        |  |

| Rangfolge                        |                                       |               |               | 1.             | 2.                                        | 3.                          |  |

Anm.: 1 Punktzahl 1 ... 5

#### 2.7. Bemerkungen zum Zielbaum

Die Summe der Wichtungsfaktoren der Haupt- und Nebenkriterien muß "1" betragen.

Berechnung der Punktbewertung: (Wichtungsfaktor 1) x (Wichtungsfaktor 2) x [Punktzahl (1 ... 5)].

Zusammenfassend sollte die ökonomische Bewertung von anwenderspezifischen Schaltkreisen in folgenden Schritten erfolgen:

- Ermittlung des Bedarfes der Anwender an anwenderspezifischen Schaltkreisen und der technischtechnologischen Möglichkeiten des Bauelementeherstellers

- . Analyse der Bedarfsentwicklung

- . Festlegung der Anforderungen an anwenderspezifische Schaltkreise

- . Realisierungsmöglichkeiten im bauelementeherstellenden Betrieb

- 2. Ermittlung der möglichen Varianten anwenderspezifischer Schaltkreise

- technische Daten der Gate-Arrays, Vollkunden- und Standardzellen-Schaltkreise

(u. a. Ausnutzung der Siliziumfläche, Ausbeute)

- Grobbilanzierung des Arbeitskräftebedarfes, des Arbeitszeitaufwandes, der Entwicklungskosten, der laufenden Kosten,