## TeleVideo TS 806, TS 806C, TS 806H, TS 806/20 and TS 806H/20 Maintenance Manual

TeleVideo Systems, Inc.

# TeleVideo® TS 806, TS 806C, TS 806H, TS 806/20 and TS 806H/20 Maintenance Manual

TeleVideo Systems, Inc. 1170 Morse Avenue Sunnyvale, California 94086 408/745-7760

#### PREFACE

This document contains reference information to be used in specifying, operating, and maintaining the TeleVideo TS 806, TS806C, TS 806H, TS 806/20, and TS 806H/20 systems. The contents of this document are copyrighted by TeleVideo Systems, Inc, 1983, and must not be photocopied, duplicated, or reproduced without the express written permission of TeleVideo Systems, Inc.

TeleVideo Systems, Inc. reserves the right to make improvements to products without incurring any obligations to incorporate such improvements in products previously sold. Specifications and information contained herein are subject to change without notice.

Send comments or suggestions on this material to the following address:

> TeleVideo Systems, Inc. Technical Documentation Department 1170 Morse Ave. Sunnyvale, CA 94086

The Zilog material in Tab Section 2 is reproduced with permission of Zilog, Inc, 1979. This material shall not be further reproduced without the written consent of Zilog, Inc.

#### CONTENTS

| Title                                                                       | Tab<br><u>Section</u> |

|-----------------------------------------------------------------------------|-----------------------|

| Computer Systems Division Limited Warranty                                  | 1                     |

| TS 806 Theory of Operation (includes TS 806H,<br>TS 806/20, and TS 806H/20) | 2                     |

| TS 806C Theory of Operation                                                 | 3                     |

| System Repair Price and Spare Parts Price Lists                             | 4                     |

| Drawings                                                                    | 5                     |

#### COMPUTER SYSTEMS DIVISION LIMITED WARRANTY

TeleVideo Systems, Inc. ("TeleVideo") warrants to its distributors, systems houses, OEMs, and national accounts ("Buyer") that products, except software, manufactured by TeleVideo are free from defects in material and workmanship. TeleVideo's obligations under this warranty are limited to repairing or replacing, at TeleVideo's option, the part or parts of the products which prove defective in material or workmanship within 180 days after shipment by TeleVideo, except that Buyer may pass along to its initial customer ("Customer") a maximum of 90 days coverage within this 180-day warranty period, provided that Buyer gives TeleVideo prompt notice of any defect and satisfactory proof thereof. Products may be returned by Buyer only after a Return Material Authorization number ("RMA") has been obtained from TeleVideo by telephone or in writing. Buyer must prepay all freight charges to return any products to the repair facility designated by TeleVideo and include the RMA number on the shipping container. TeleVideo will deliver replacements for defective products or parts on an exchange basis to Buyer, freight prepaid to the Buyer or the Customer. Products returned to TeleVideo under this warranty become the property of TeleVideo. With respect to any product or part thereof not manufactured by TeleVideo, only the warranty, if any, given by the manufacturer thereof, applies.

#### **EXCLUSIONS:**

This limited warranty does not cover losses or damage which occurs in shipment to or from Buyer or Customer, or is due to, (1) improper installation or maintenance, misuse, neglect or any cause other than ordinary commercial or industrial application, or (2) adjustment, repair or modification by other than TeleVideoauthorized personnel, or (3) improper environment, excessive or inadequate heating or air conditioning and electrical power failures, surges, or other irregularities, or (4) any statement made about TeleVideo's products by salesmen, dealers, distributors or agents, unless confirmed in writing by a TeleVideo officer.

THE FOREGOING TELEVIDEO LIMITED WARRANTY IS IN LIEU OF ALL OTHER WARRANTIES, WHETHER ORAL, WRITTEN, EXPRESS, IMPLIED OR STATUTORY. IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE DO NOT APPLY. TELEVIDEO'S WARRANTY OBLIGATIONS AND DISTRIBUTOR'S REMEDIES HEREUNDER ARE SOLELY AND EXCLUSIVELY AS STATED HEREIN. TELEVIDEO MAKES NO WARRANTY WHATSOEVER CONCERNING ANY SOFTWARE PRODUCTS, WHICH ARE SOLD "AS IS" AND "WITH ALL FAULTS". TELEVIDEO'S LIABILITY, WHETHER BASED ON CONTRACT, TORT, WARRANTY, STRICT LIABILITY OR ANY OTHER THEORY, SHALL NOT EXCEED THE PRICE OF THE INDIVIDUAL UNIT WHOSE DEFECT OR DAMAGE IS THE BASIS OF THE CLAIM. IN NO EVENT SHALL TELEVIDEO BE LIABLE FOR ANY LOSS OF PROFITS, LOSS OF USE OF FACILITIES OR EQUIPMENT, OR OTHER INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

#### TS-806 THEORY OF OPERATION

This theory of operation describes the hardware layout, functions and operations.

#### TABLE OF CONTENTS

| Section | Title                   |

|---------|-------------------------|

| 1.0     | Introduction            |

| 2.0     | General Description     |

| 3.0     | Function                |

| 4.0     | Circuit Description     |

| 5.0     | Connector Configuration |

| 6.0     | Jumper Description      |

| 7.0     | Power Requirements      |

| 8.0     | WDC                     |

#### 1. INTRODUCTION

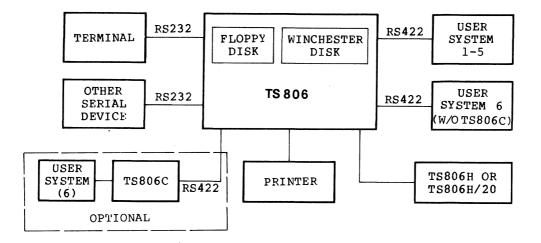

The TS-806 is a multi-user system that supports up to 6 user stations. The user stations may be configured from TS-800, TS-801, or TS802-series systems.

The TS-806 is a single board microcomputer based on the Z80A family of microprocessor components. The system functions a central resource manager in a multi-user environment through RS-422 SDLC control. The terminal used with the TS-806 is a standard TeleVideo terminal used as a service terminal.

The TS806 contains a 10-megabyte Winchester technology hard disk drive. The TS806/20 uses a 20-megabyte Winchester drive in the same style cabinet as the TS806. Both systems use the WD-1000 disk interface board. The TS806 can be expanded with the TS-806H, and the TS806/20 is expanded with the TS806H/20.

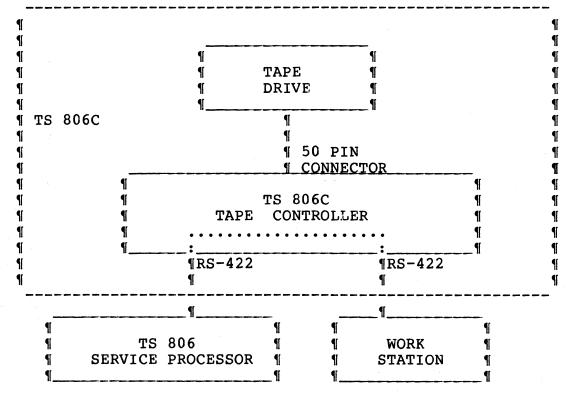

The TS806C is a magnetic cartridge option to the TS806-series systems. The TS806C is interfaced to the TS806-series system through one of the RS-422 high speed serial data links used for a user station. A user station can be connected to the TS806C as shown in the block diagram to allow the full compliment of 6 stations.

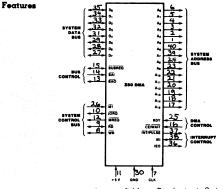

#### 2. GENERAL DESCRIPTION

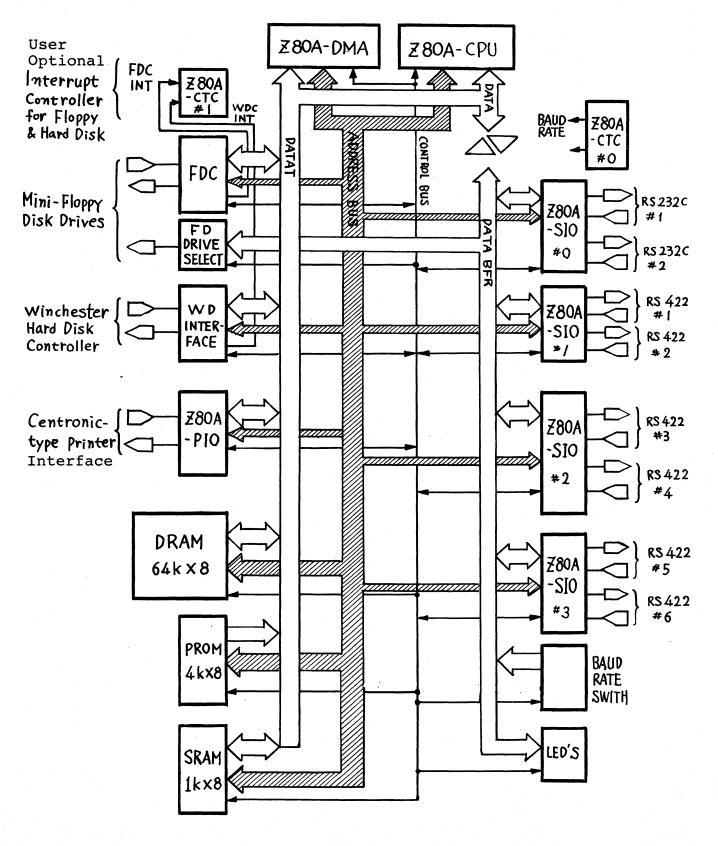

a. Z80A-CPU

The main processing unit in the system (4.0 MHz operation).

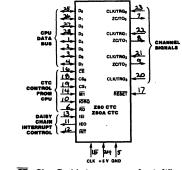

b. Z80A-CTC

Counter/timer chip, generating the baud rate for RS232C serial channel.

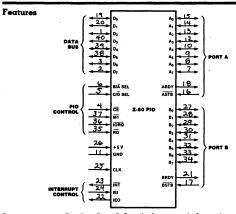

c. Z80A-PIO

Parallel I/O chip, provides centronics-type printer interface.

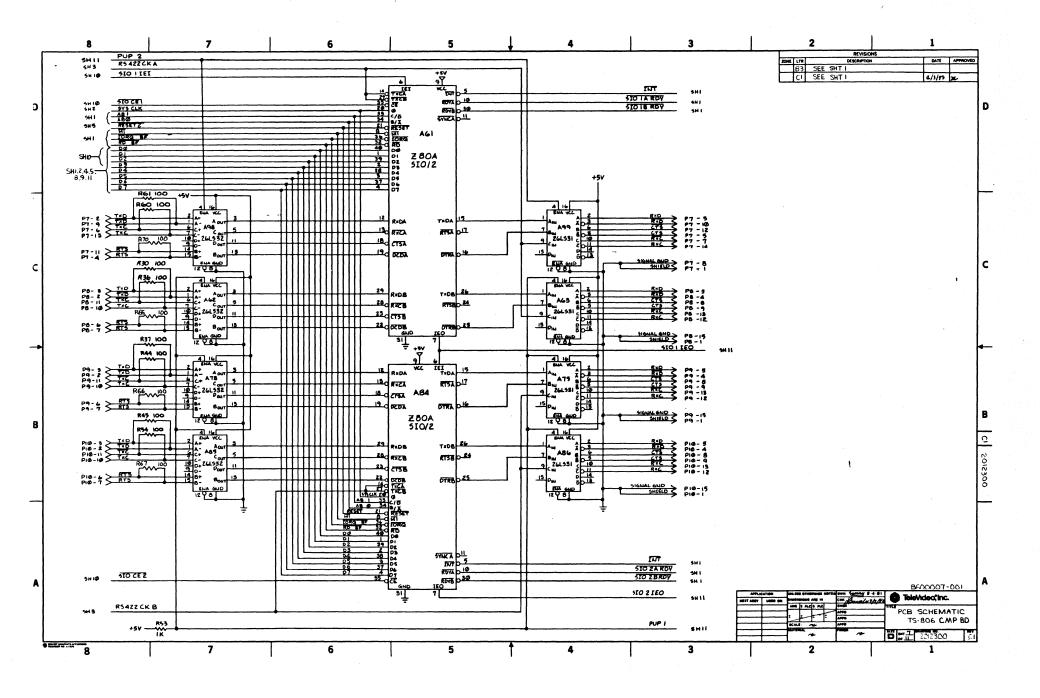

d. Z80A-SIO

Serial I/O chips, providing RS232C interface (data rate to 19.2 KB) and/or RS422 high-speed serial interface with data rate of 800K bit/sec.

e. Z80A-DMA

Direct memory access controller chip is used for direct transfer of data between memory and peripheral I/O like floppy disk, Winchester hard disk, etc.

f. Memory

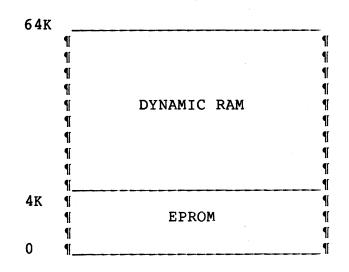

Main memory available to user is 64K bytes, using 64K X 1 DRAM 4K bytes of ROM and 1K byte of SRAM are used for system firmware (used on power up or reset only).

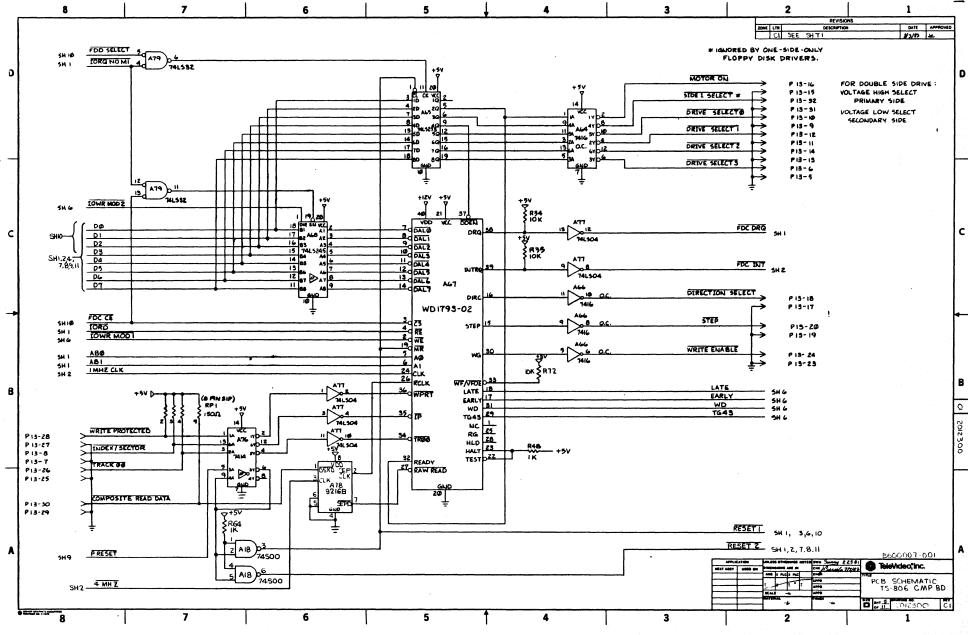

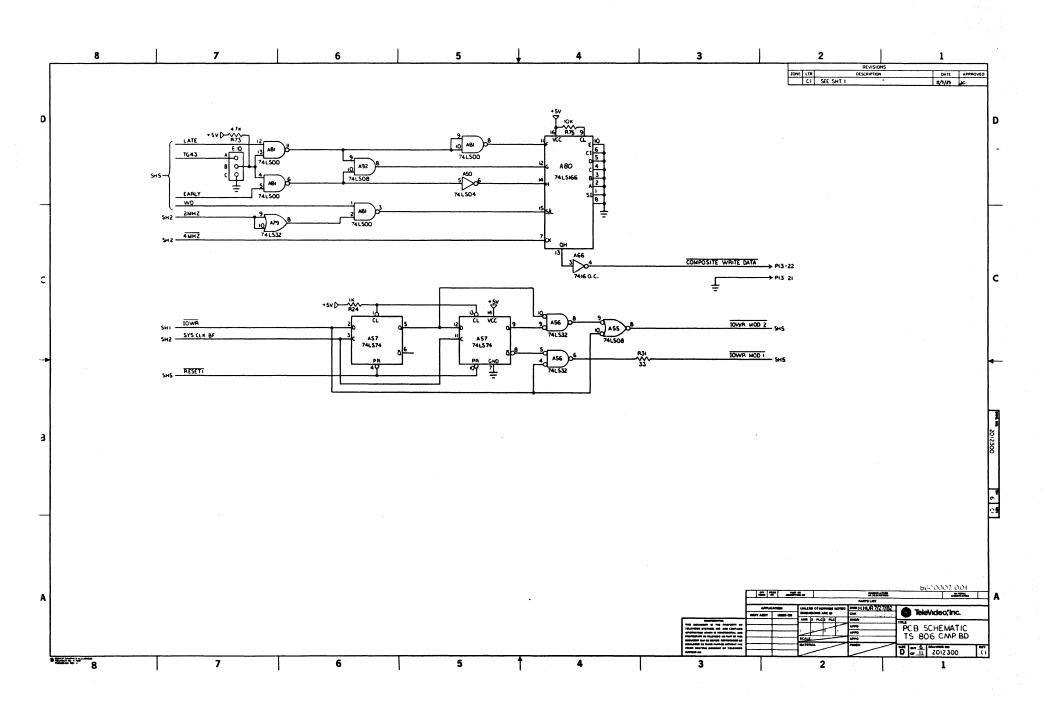

g. Floppy disk controller

Western Digital's FD 1793 chip along with its support chips WD 2143-01 and WD1691 provides control and interface to the 5  $\frac{1}{4}$ " floppy drive.

h. Winchester hard disk interface

Interface is provided to the disk controller board for the 5  $\frac{1}{4}$ " hard disk.

#### 3. FUNCTION

The facilities available to the users are 64K bytes of main memory, floppy disk controller which can drive potentially up to 4 drives (0.5M byte each), interface to communicate with the hard disk controller which can also drive potentially up to 4 hard disk drives 5 ¼" Winchester, and parallel port for high-speed centronics-type printer interface.

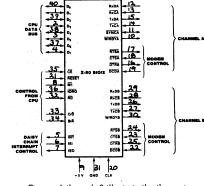

2 channels of RS232C type interface (from 1 SIO), and 6 channels of RS422 interface (from the other 3 SIO's) to communicate with the user systems (TS-800, TS-801) are provided.

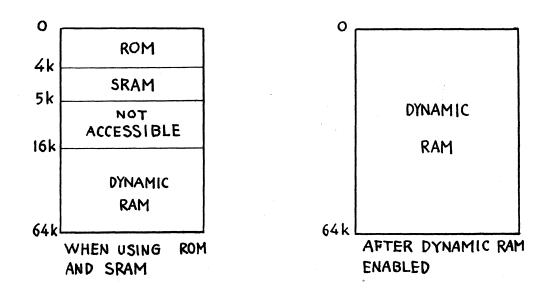

4K bytes of ROM and 1K bytes of SRAM are used for system initialization, diagnostics, boot, and floppy/hard disk control during the power-up or reset, and are not accessible by the users. After the initial program in the ROM is run upon power-up or reset, the dynamic memory area (address 00-16 K hex.) is switched on so that the whole 64K byte of main memory can be used by the user.

TS-806 uses a DMA controller to transfer data between memory and I/O devices, memory to memory, and also I/O device to I/O device.

A CTC chip (A40) is reserved to provide vectored interrupt capability. Another CTC chip (A39) generates (switch-selectable) baud rates for RS232C interface. 2 Channels of this CTC are reserved for time-of-day generation as a user implemented option.

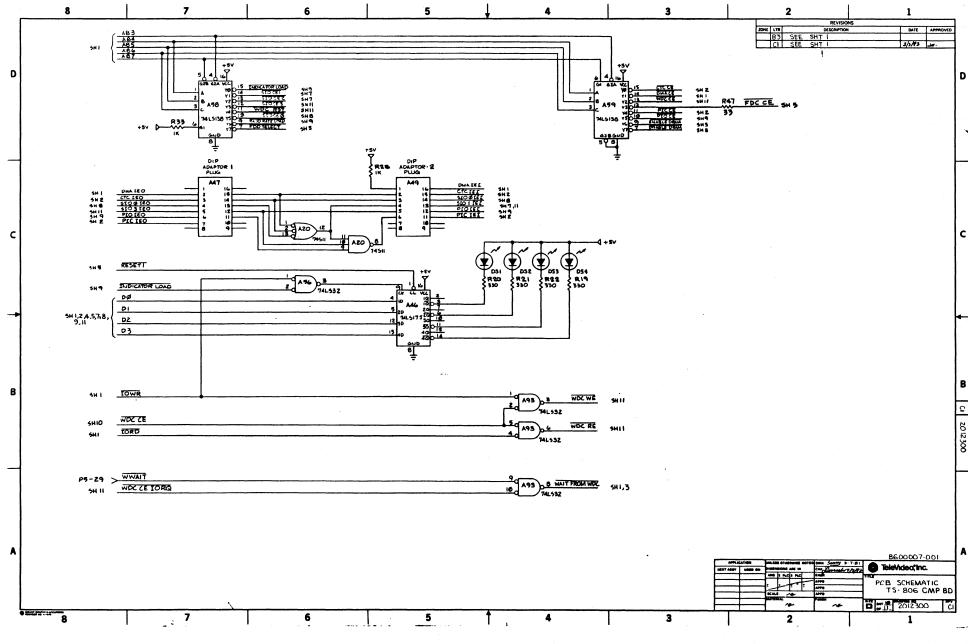

4 LED indicators are used for diagnostic purposes to indicate faults in the hardware.

The system block diagram is shown in Figure 2, I/O port assignment is shown in Table 1 and the baud rate switch configuration is shown in Table 2.

DIAGRAM 2 - BLOCK DESIGN OF TS-806

ABUS BIT #

## I/O PORT

| - |     |   |   |          |   |   |   |      |                                         |

|---|-----|---|---|----------|---|---|---|------|-----------------------------------------|

| 7 | 6   | 5 | 4 | 3        | 2 | 1 | 0 | HEX. |                                         |

| 0 | 0   | 0 | 0 | 0        | х | x | х | 00   | Indicator Load (LED Ref.)               |

| 0 | 0   | 0 | 1 | 0        | х | 0 | 0 | 10   | SIO 1, Ch A Data Reg.                   |

|   |     |   |   |          |   | 1 | 0 | 12   | Com/Stat Reg                            |

|   |     |   |   |          |   | 0 | 1 | 11   | Ch B Data Reg.                          |

|   |     |   |   |          |   | 1 | 1 | 13   | Com/Stat Reg                            |

| 0 | 0   | 1 | 0 | 0        | х | 0 | 0 | 20   | SIO 2, Ch A Data Reg.                   |

|   |     |   |   |          |   | 1 | 0 | 22   | Com/Stat Reg                            |

|   |     |   |   |          |   | 0 | 1 | 21   | Ch B Data Reg.                          |

|   |     |   |   |          |   | 1 | 1 | 23   | Com/Stat Reg                            |

| 0 | 0   | 1 | 1 | 0        | х | 0 | 0 | 30   | SIO 3, Ch A Data Reg.                   |

|   |     |   |   |          |   | 1 | 0 | 32   | Com/Stat Reg                            |

|   |     |   |   |          |   | 0 | 1 | 31   | Ch B Data Reg.                          |

|   |     |   |   |          |   | 1 | 1 | 33   | Com/Stat Reg                            |

| 0 | 1   | 0 | 0 | 0        | х | х | х | 40   | WDC Reset (Winchester Disk Soft Reset)  |

| 0 | 1   | 0 | 1 | <b>0</b> | Х | 0 | 0 | 50   | SIO 0, Ch A Data Reg.                   |

|   |     |   |   |          |   | 1 | 0 | 52   | Com/Stat Reg                            |

|   | - , |   |   |          |   | 0 | 1 | 51   | Ch B Data Reg.                          |

|   |     |   |   |          |   | 1 | 1 | 53   | Com/Stat Reg                            |

| 0 | 1   | 1 | 0 | 0        | Х | Х | Х | 60   | Baud Rate Load                          |

| 0 | 1   | 1 | 1 | 0        | х | Х | Х | 70   | FDD Select                              |

| 1 | 0   | 0 | 0 | 0        | X | 0 | 0 | 80   | CTC Ch 0                                |

|   |     |   |   |          |   | 0 | 1 | 81   | Ch 1                                    |

|   |     |   |   |          |   | 1 | Q | 82   | Ch 2                                    |

|   |     |   |   |          |   | 1 | 1 | 83   | Ch 3                                    |

| 1 | 0   | 0 | 1 | 0        | Х | X | х | 90   | DMA                                     |

| 1 | 0   | 1 | 0 | 0        | 0 | 0 | 0 | A0   | WDC Reg. 0 Data Reg.                    |

|   |     |   |   |          | 0 | 0 | 1 | Al   | Reg. 1 Error/Write Precompensation Reg. |

|   |     |   |   |          | 0 | 1 | 0 | A2   | Reg. 2 Sector Count Reg.                |

|   |     |   |   |          | 0 | 1 | 1 | A3   | Reg. 3 Sector Number Reg.               |

|   |     |   |   |          | 1 | 0 | 0 | A4   | Reg. 4 Cylinder Low Reg.                |

|   |     |   |   |          | 1 | 0 | 1 | A5   | Reg. 5 Cylinder High Reg.               |

|   |     |   |   |          | 1 | 1 | 0 | A6   | Reg. 6 Size/Drive/Head Reg.             |

|   |     |   |   |          | 1 | 1 | 1 | A7   | Reg. 7 Status/Command Reg.              |

|   |     |   |   |          |   |   |   |      |                                         |

ABUS BIT #

I/O PORT

| 7  | 6 | 5 | 4 | 3 | 2 | 1 |   | HEX. |                            |

|----|---|---|---|---|---|---|---|------|----------------------------|

| 1  | 0 | 1 | 1 | 0 | Х | 0 | 0 | в0   | FDC Com/Stat Reg.          |

|    |   |   |   |   |   | 0 | 1 | Bl   | Track Reg.                 |

|    |   |   |   |   |   | 1 | 0 | В2   | Sector Reg.                |

|    |   |   |   |   |   | 1 | 1 | В3   | Data Reg.                  |

| 1  | 1 | 0 | 0 | 0 | х | 0 | 0 | CO   | PIC Ch 0 (CTC) User Option |

|    |   |   |   |   |   | 0 | 1 | Cl   | Ch 1                       |

|    |   |   |   |   |   | 1 | 0 | C2   | Ch 2                       |

|    |   |   |   |   |   | 1 | 1 | C3   | Ch 3                       |

| 1  | 1 | 0 | 1 | 0 | x | 0 | 0 | D0   | PIO Ch A Data Reg.         |

|    |   |   |   |   | • | 1 | 0 | D2   | Com/Stat Reg               |

|    |   |   |   |   |   | 0 | 1 | Dl   | Ch B Data Reg.             |

|    |   |   |   |   |   | 1 | 1 | D3   | Com/Stat Reg               |

| 1  | 1 | 1 | 0 | 0 | X | х | х | EO   | Enable Dram                |

| 1. | 1 | 1 | 1 | 0 | Х | Х | Х | FO   | Disable Dram               |

|    |   |   |   |   |   |   |   |      |                            |

Table 1. I/O Port Assignment

#### Baud Rate Generation for SIO:

Switches for baud rates are upper 4 dip switches which can be set up as following table.

|      |       | Sw | itc | h P | os. |

|------|-------|----|-----|-----|-----|

| Baud | Rate  | 4  | 3   | 2   | 1   |

|      |       |    |     |     |     |

| 19.2 | KBaud | 0  | 0   | 0   | 0   |

| 9.6  | KBaud | 0  | 0   | 0   | 1   |

| 4.8  | KBaud | 0  | 0   | 1   | 0   |

| 2.4  | KBaud | 0  | 0   | 1   | 1   |

| 1.2  | KBaud | 0  | 1   | 0   | 0   |

| 600  | Baud  | 0  | 1   | 0   | 1   |

| 300  | Baud  | 0  | 1   | 1   | 0   |

| 150  | Baud  | 0  | 1   | 1   | 1   |

| 75   | Baud  | 1  | 0   | 0   | 0   |

Table 2. Baud Rate Switch

#### Dip Switch Description:

0 (Close) / 1 (Open)

| SW | 1: | Baud     | Rate | 9          |

|----|----|----------|------|------------|

|    | 2: | · · · ·  |      |            |

|    | 3: | "        |      |            |

|    | 4: | "        |      |            |

|    | 5: | Unused   |      |            |

|    | 6: | Unused   |      |            |

|    | 7: | Unused   |      |            |

|    | 8: | Reserved | for  | Diagnostic |

#### 4. Circuit Description

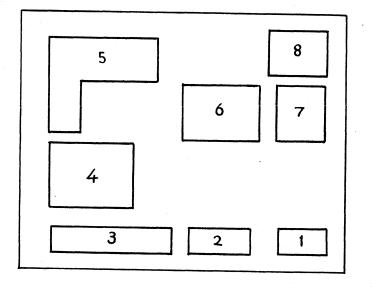

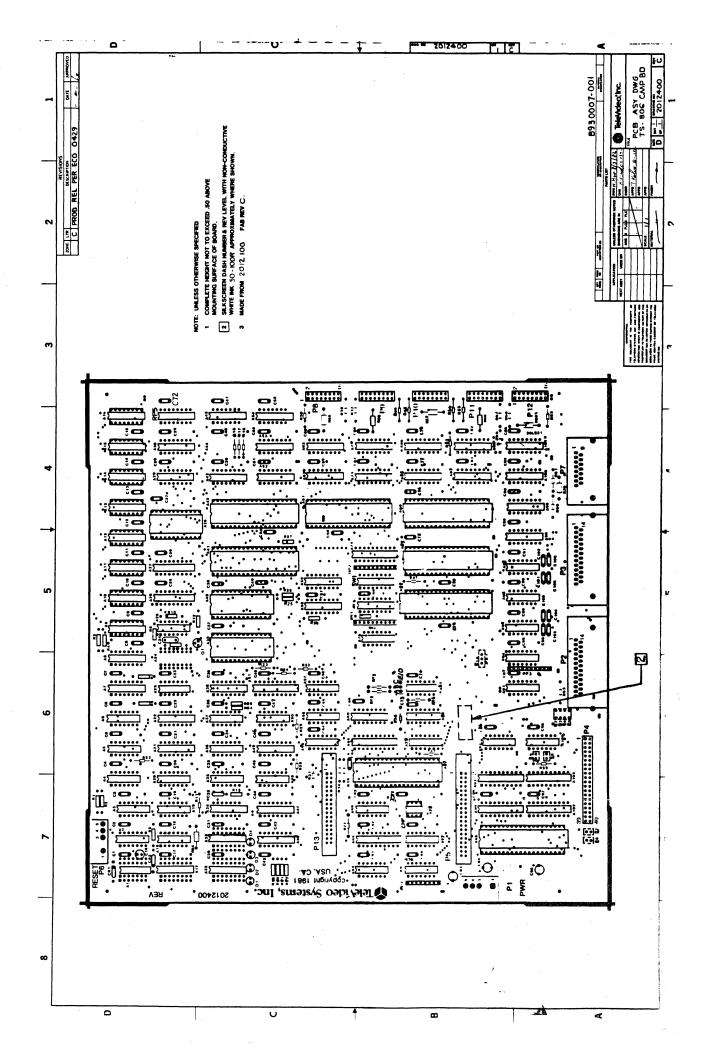

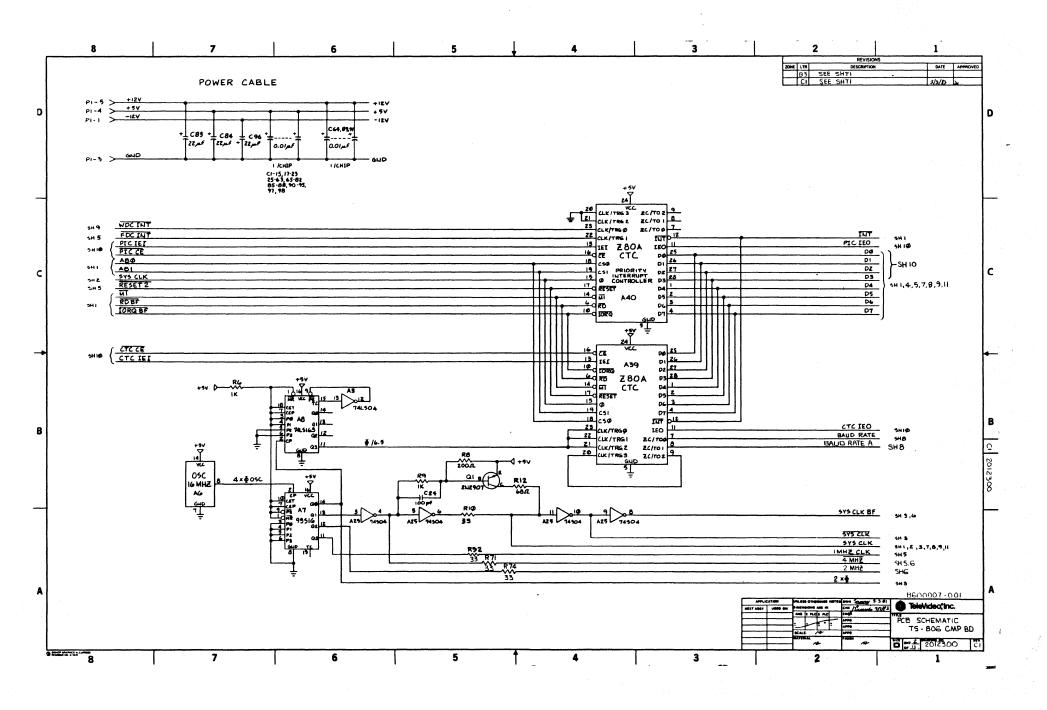

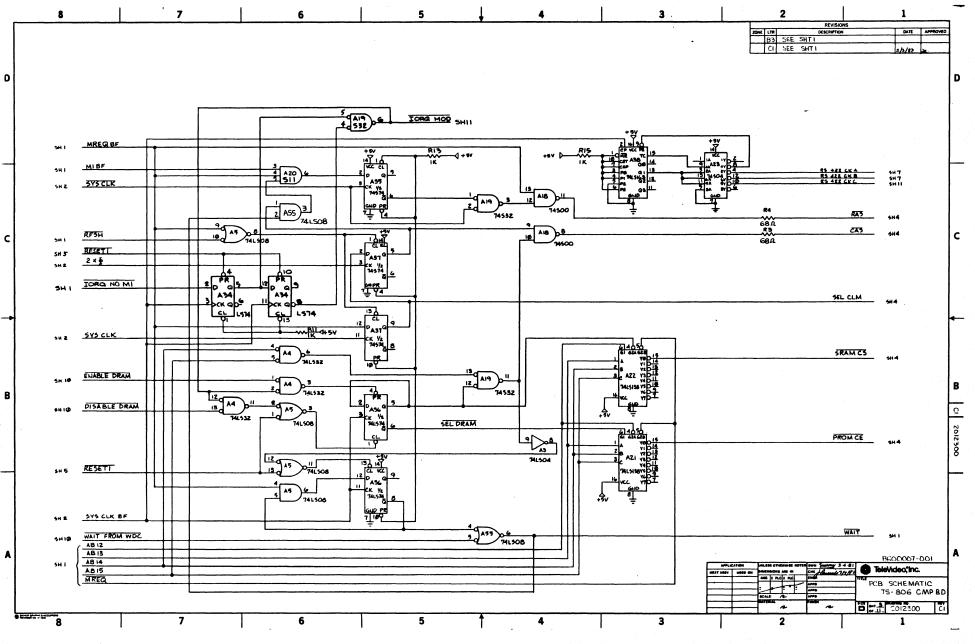

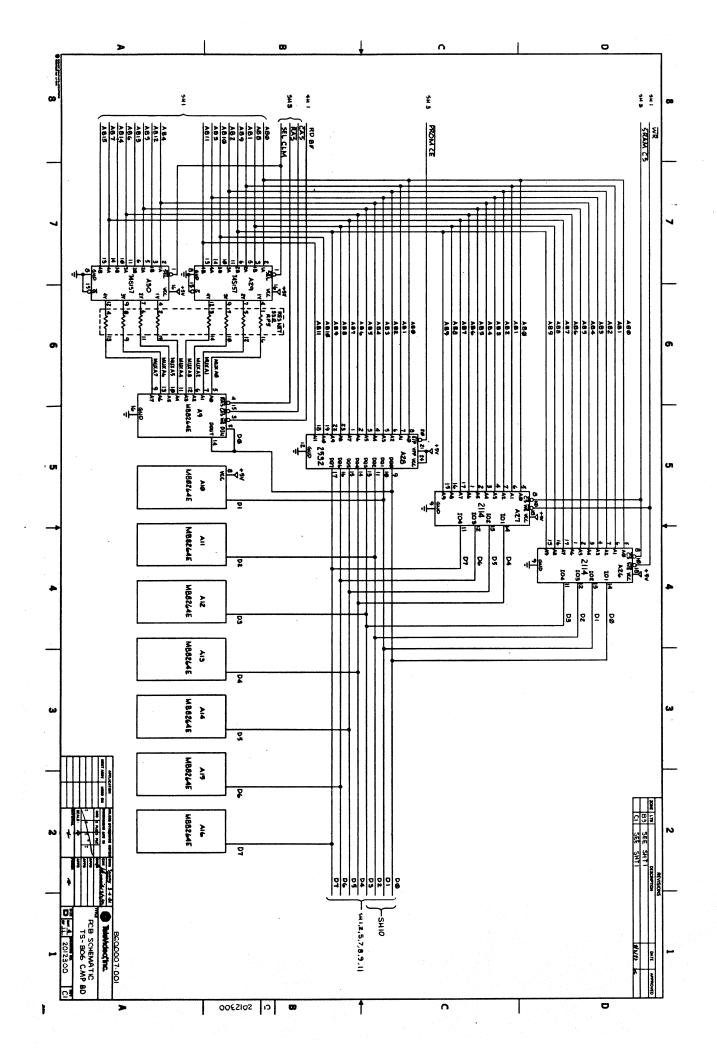

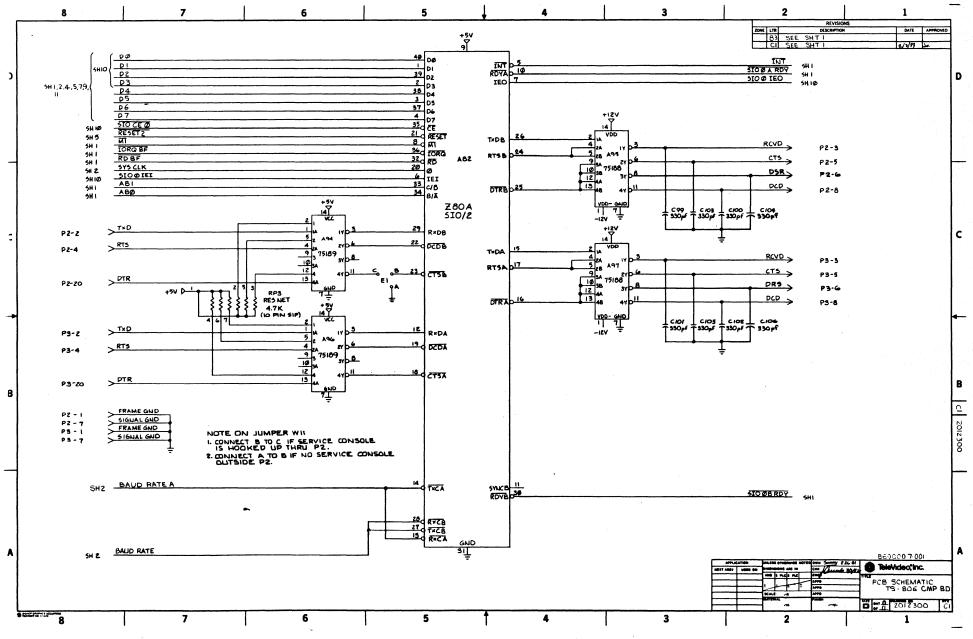

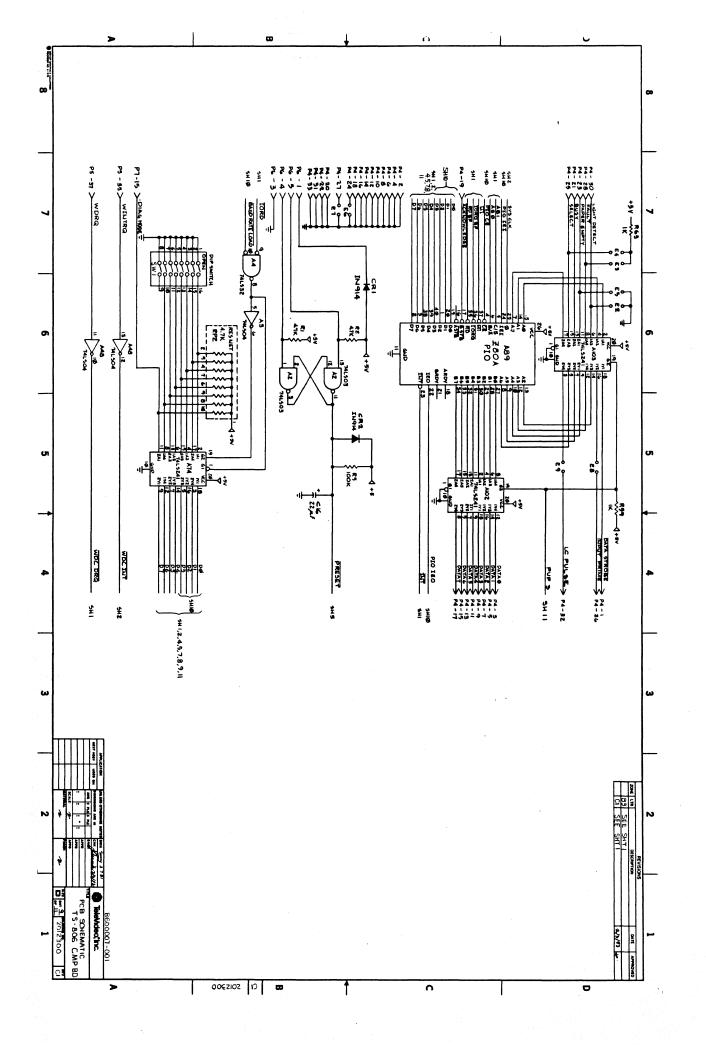

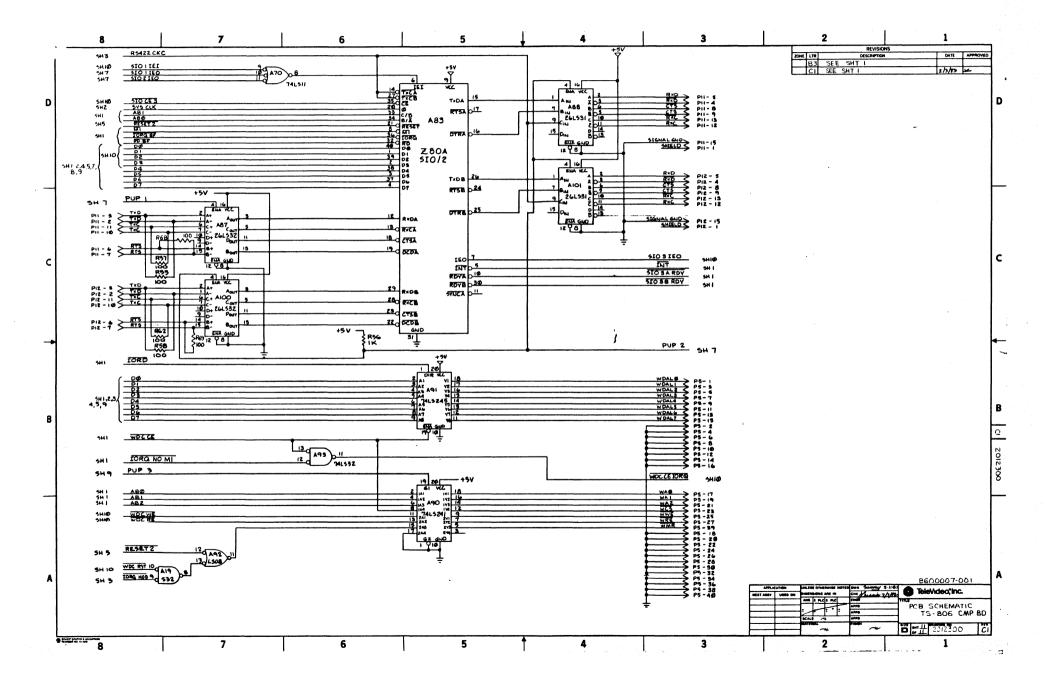

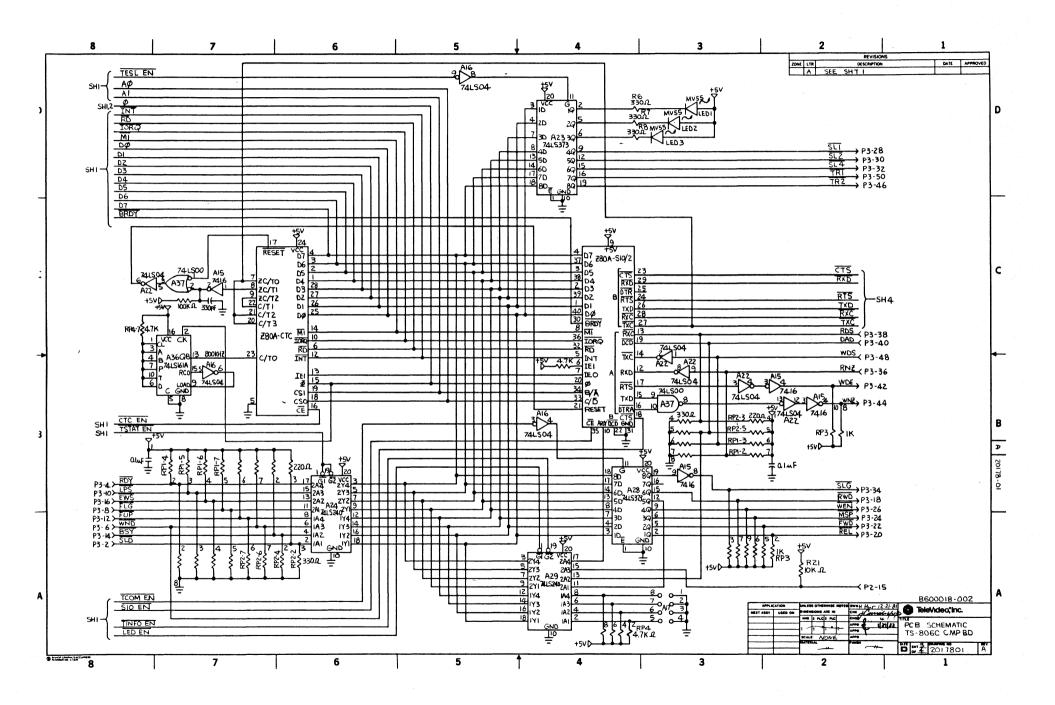

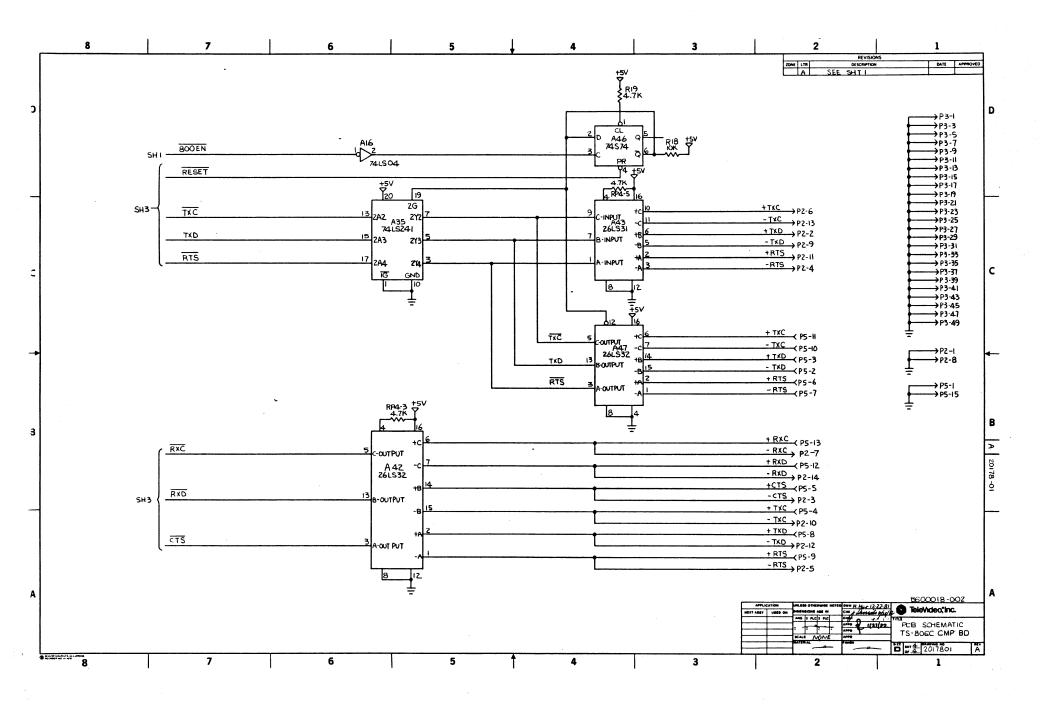

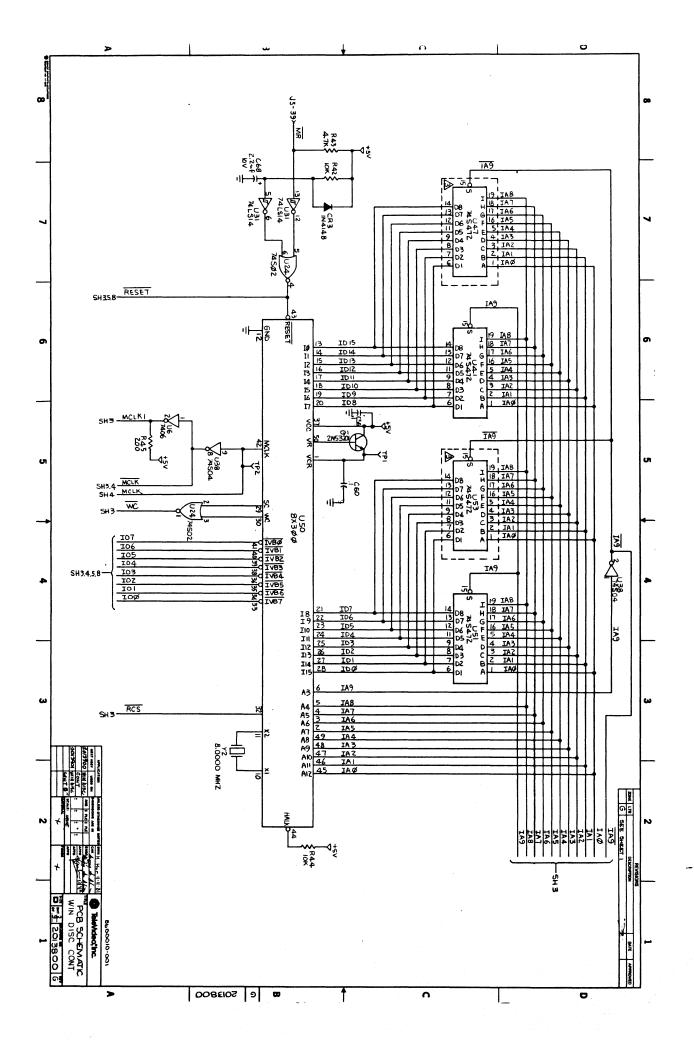

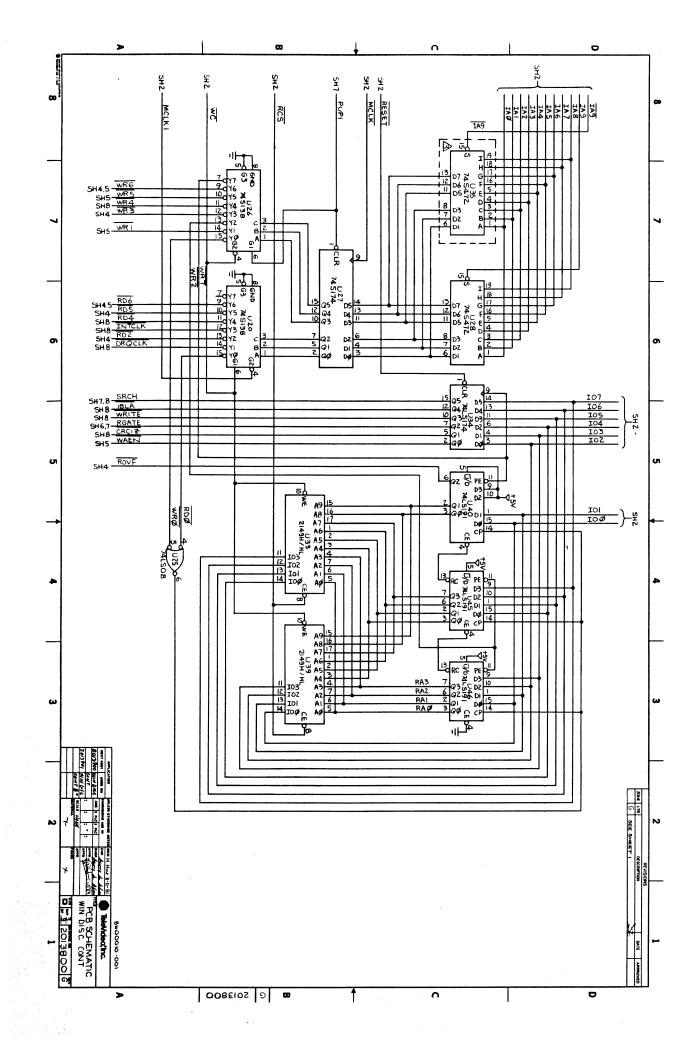

Generally TS-806 circuitry can be divided into 8 sections as shown in Figure 3.

1. Reset

2. Clock

3. Memory

- 4. CPU & DMA

- 5. Serial I/O

6. Floppy Disk Control

7. Hard Disk Controller

8. Printer Interface

#### Figure 3 System Board Description

#### 4.1 Reset

The chip associated with the reset circuit is a 74LS00 (A2), which debounces the reset signal when the reset switch is pressed.

A2-13 is normally low and Pin 1 is normally high. -Reset must be active for at least three clock cycles to properly reset the CPU. As long as -Reset remains active, the address and data bus float, and the control signal outputs are inactive.

The CPU returns to normal operation after two internal "T" cycles. -Reset clears the PC register so the register now contains a value of 0000.

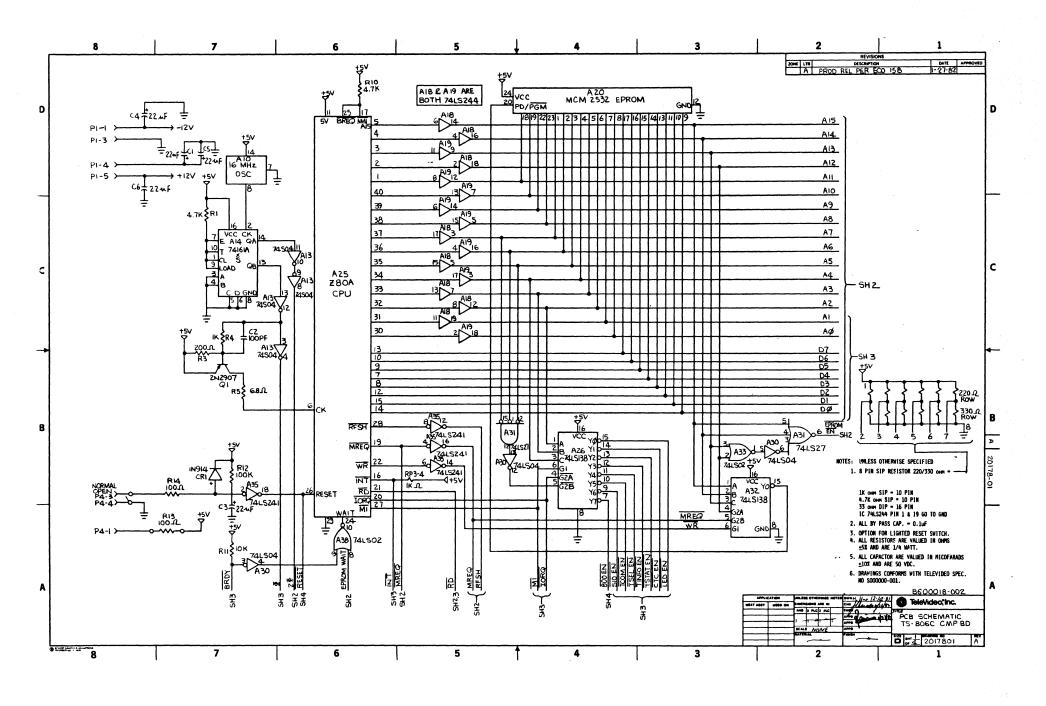

#### 4.2 Clock Generation

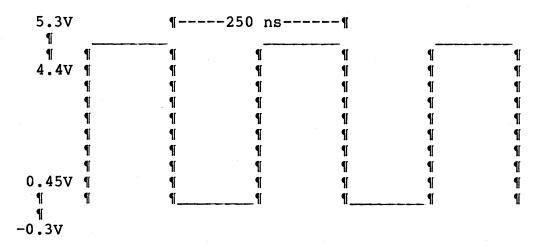

16 MHz signal from the oscillator (OSC) is divided down to a 4 MHz signal using a 93S16 (A7) and TR 2N2907 is used to drive the proper system clock level and again buffered for enough driving current.

The 1 MHz clock from the 93S16 is supplied to the floppy disk controller chip (FD 1793). To generate the baud rate, the 8 MHz signal from the 93S16 is fed into a 74LS163 (A8), to generate the frequency of 1/6.5 times the system clock for the CTC. Transmit clock for the SIO (RS422) is generated through another 74LS163 (A38) and 74S04 (A23) using system clock.

#### 4.3 Memory

ROM and Static RAM:

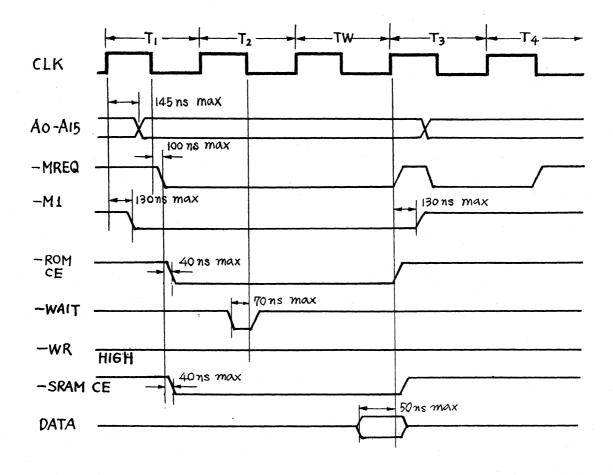

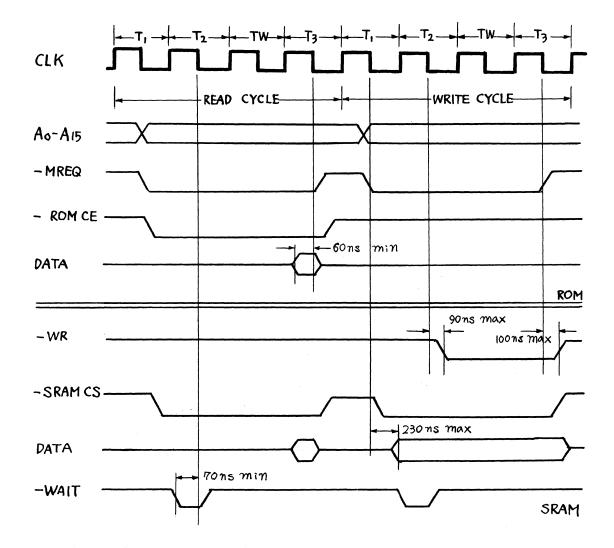

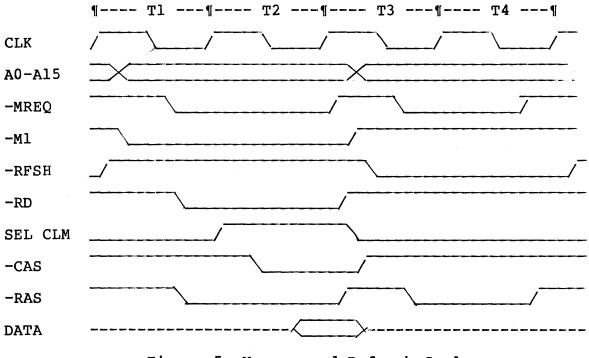

A single 4K X 8 ROM and two 1K X 4 SRAM are used. ROM and SRAM are enabled upon power-up or reset. The enabling circuitry is composed of two 74LS138 (A21, A22) and other necessary chips of flip-flop and gates. By issuing an I/O instruction, we can either enable or disable the ROM and SRAM. When the ROM and SRAM are enabled, -CAS signal for dynamic RAM column address goes inactive disabling dynamic RAM (00H-16KH), so only ROM and SRAM are active. During read/write operations involving ROM and SRAM the 74LS74 (A36) generates one wait state to allow sufficient time for the read/write operation.

Figure 4 Memory Space Description

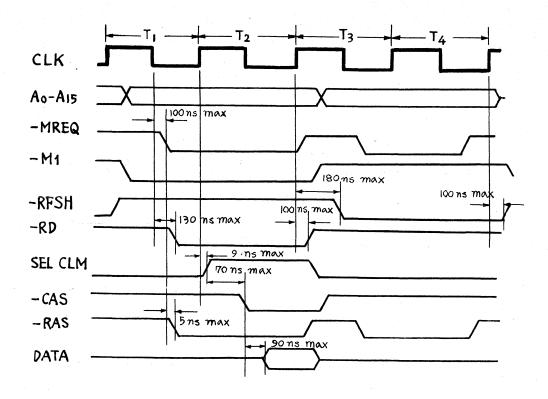

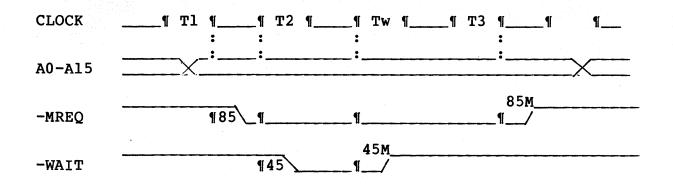

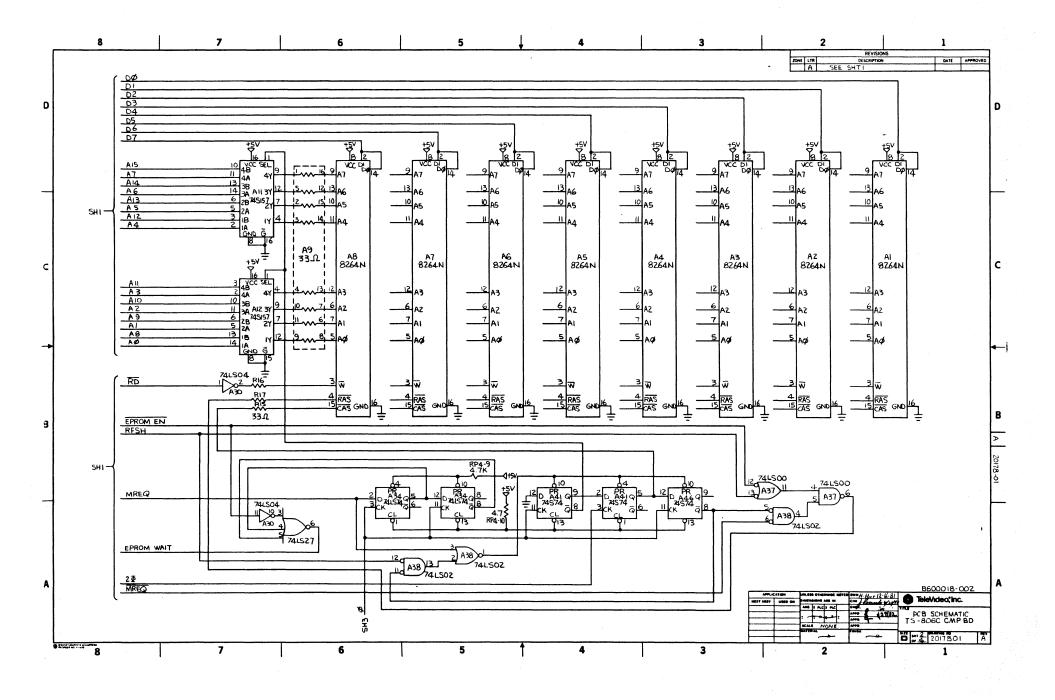

4.3 Eight DRAM chips (64Kb each) are used for main memory. Two 74S74 (A35,A37) and other related chips (A18, A19) are used to generate -CAS and -RAS signals using -M1 and -MREQ signals. Select column signal chooses either A0-A7 or A8-A15 as row and column address. As explained previously, when dynamic RAM is enabled it activiates -CAS signal so that all DRAM locations can be accessed by the user. During refresh, only -RAS signal is activated and one whole row is refreshed at one time.

The following diagrams show the timing of those signals.

Figure 5 Instruction Fetch from ROM/SRAM

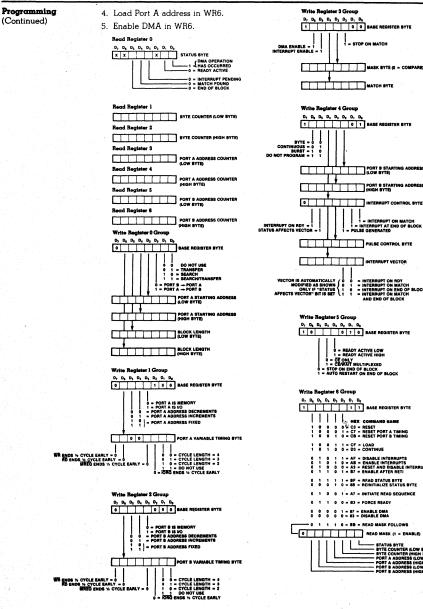

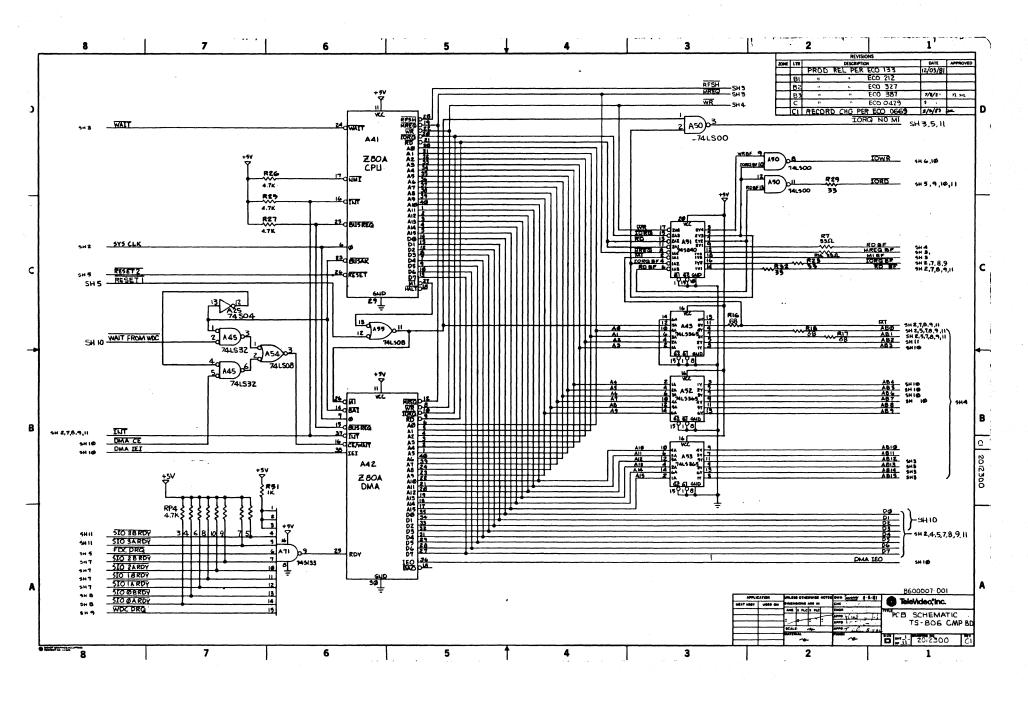

#### 4.4 DMA Operation

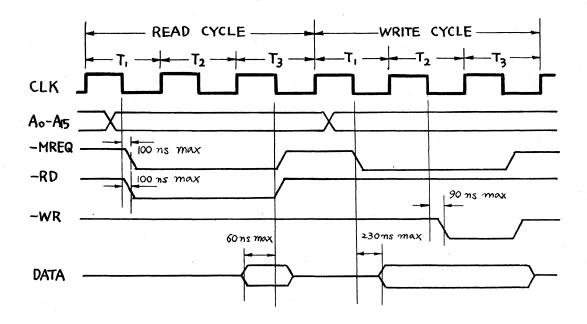

The RDY line is monitored by the DMA to determine when a peripheral device is ready for read or write operation. When the DMA is enabled the RDY line indirectly controls DMA activity. -BUSREQ is used as output from the DMA chip to request for control of the address, data and control bus from the CPU. If CPU receives active -BUSREQ, the CPU will set these buses to high impedance state as soon as the current CPU machine cycle is terminated, and then sends out -BUSAK signal to indicate that DMA can control these signals.

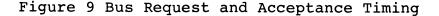

Figure 9 illustrates the -BUSREQ and -BUSAK (BAI) timing. The RDY line is sampled on every rising edge of CLK as a level, not an edge. When the DMA detects a low on -BAI line for two consecutive rising edges of CLK, the DMA begins transferring data on the next rising edge of CLK.

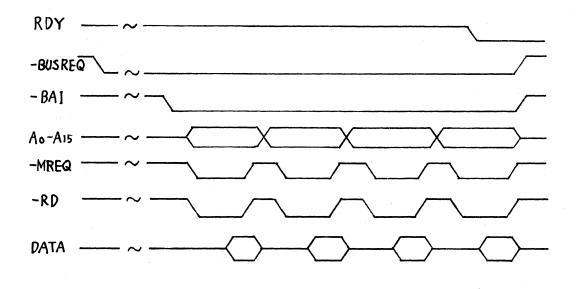

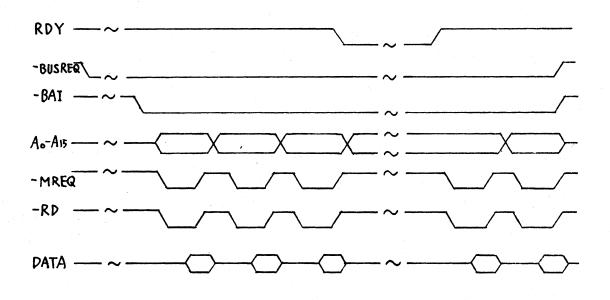

Figure 10 and Figure 11 explain the timing diagram of RDY line in burst mode and in continuous mode of the DMA.

Figure 10 RDY Line in Burst Mode (Refer to I/O Operation for precise timing.)

Figure 11 RDY Line in Continuous Mode (Refer to I/O Operation for precise timing)

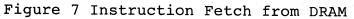

#### 4.5 I/O Operation

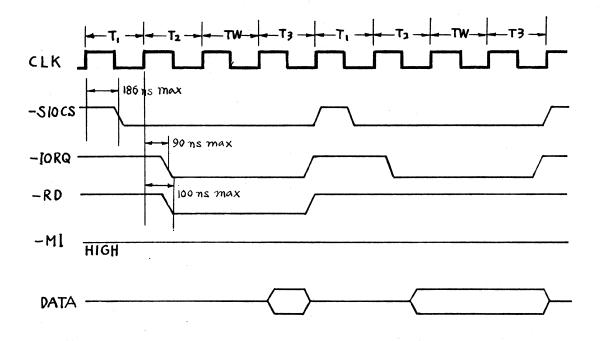

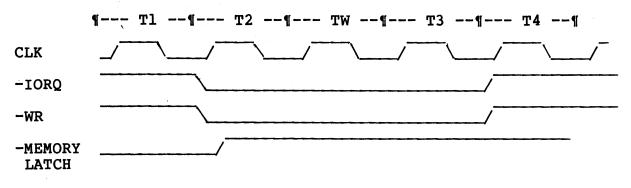

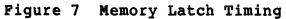

The Z80A CPU can address up to 256 I/O ports. The CPU uses only the lower 8 address lines for I/O addressing. The address lines A3 to A7 are decoded through two 74LS138 (A58,59). For I/O read/write, the -IORQ signal "NANDED" with RD/WR is used to provide -IORD/-IOWR signal. During the I/O operation, the CPU automatically inserts a single wait state (TW). This extra wait state allows sufficient time for an I/O port to complete a read/write operation.

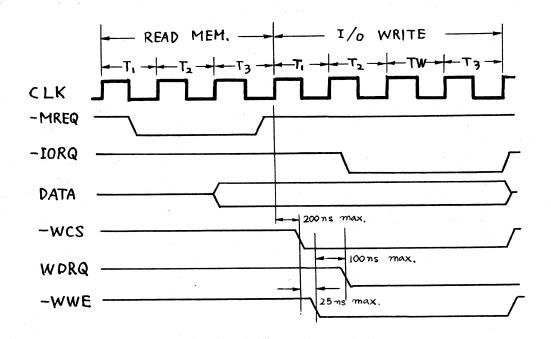

One SIO (A82) is for RS232 interfaces and its related chips are 75188 (for output) and 75189 (for input). The other 3 SIO's (A61, A83, A84) are for RS422 interfaces with the user system; the related chips are 26LS31 (for output) and 26LS32 (for input). The timing of the signals generated by the CPU input instruction (to read data or the status byte) and output instruction (to write data or control bytes) are illustrated in Figure 12.

#### 4.5 I/O Operation

FD 1793, WD1691, WD2143-01 and other related chips are used for floppy disk control. FD 1793 has two modes of operation according to the state of -DDEN (Pin 37). When -DDEN=1, single density is selected. The CLK input (Pin 24) is set at 1 MHz for mini floppy. DRQ line indicates that the data register contains assembled data in the read operation, or the data register is empty in the write operation. This signal is reset when serviced by the system through reading or loading the data register.

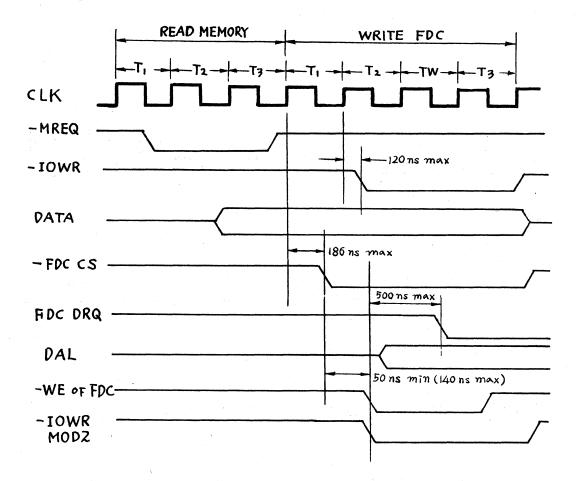

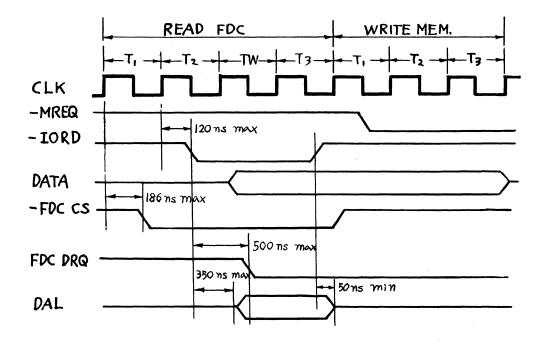

Figure 13 and 14 show timing diagram of those related signals.

Figure 13 Timing Diagram of Memory to FDC Transfer (DMA Write Operation)

Figure 14 Timing Diagram of FDC to Memory Transfer (DMA read operation)

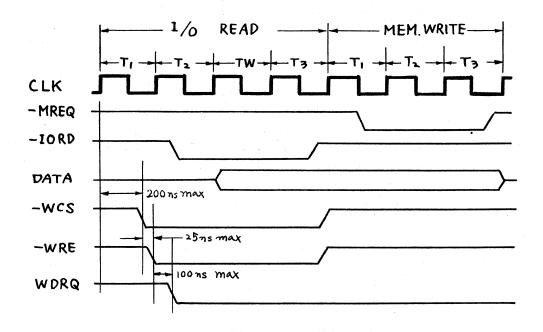

WD 1000 controller board is used for  $5\frac{1}{4}$ " Winchester disk interface. As with the floppy disk controller, -WDC DRQ signal is used to control the RDY line of DMA by being "NANDED" with other I/O RDY signals through 74S133 (A71). -IORD signal decides the direction of data on 74LS245 (A91) between the system and controller. Figure 15 and 16 shows the timing diagram in WDC read/write operation using DMA.

Figure 16 Memory to WDC Transfer (DMA Write Operation)

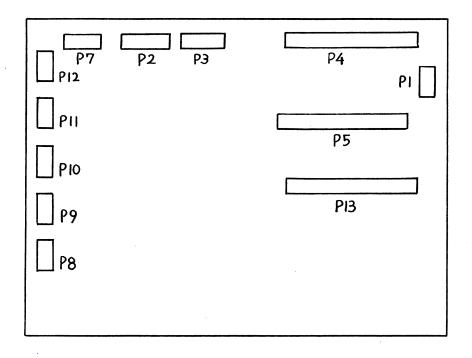

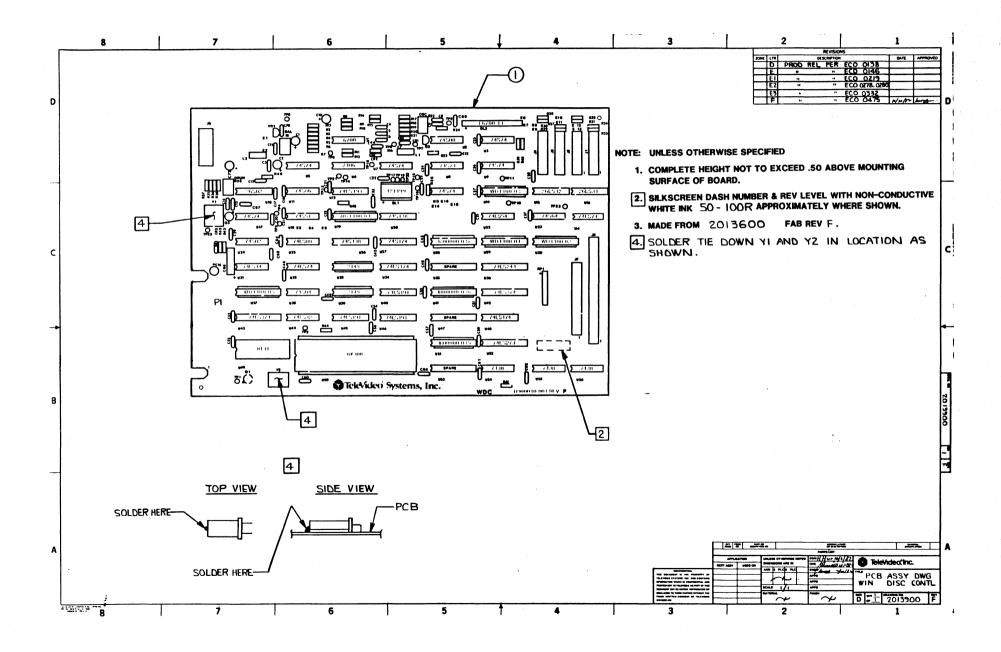

## 5. Connector Description

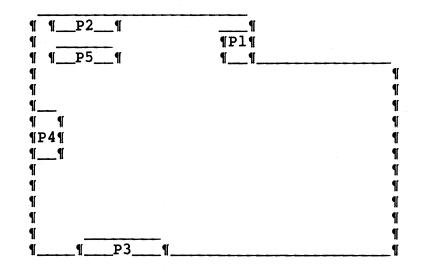

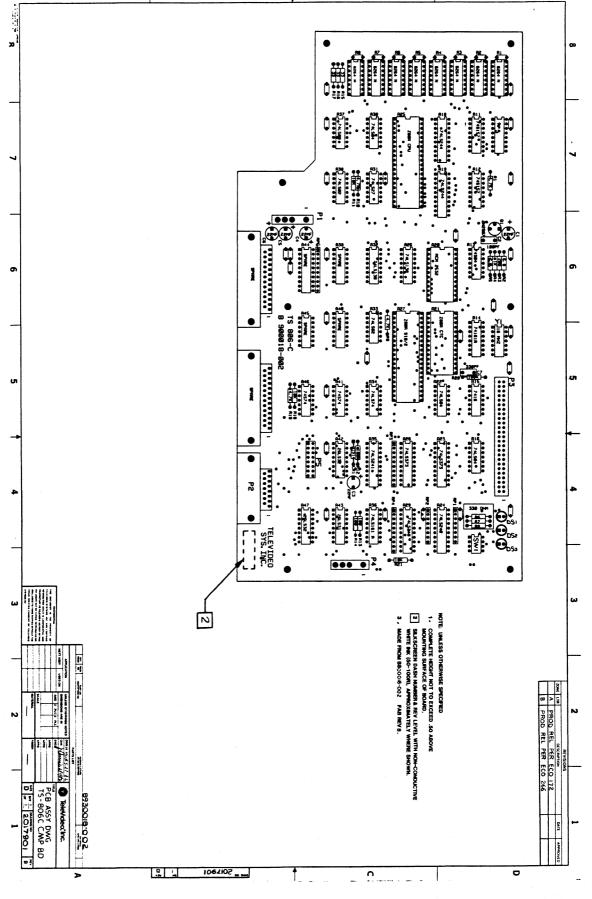

All the connector position is shown in Figure 17 and Table 3.

Figure 17 Connectors on the board

| Connector # | Description                          |

|-------------|--------------------------------------|

| P1          | Power                                |

| P2          | RS232C Service Terminal Interface    |

| P3          | RS232C Serial Interface              |

| P4          | Centronics-type Printer Interface    |

| P5          | Winchester Disk Controller Interface |

| P6          | Reset, Power On Light                |

| P7          | RS422 User Channel 1                 |

| P8          | RS422 User Channel 2                 |

| P9          | RS422 User Channel 3                 |

| P10         | RS422 User Channel 4                 |

| P11         | RS422 User Channel 5                 |

| P12         | RS422 User Channel 6                 |

| P13         | Floppy Disk Drive Interface          |

#### Table 3. Connector Assignment

#### 5.1 Power Connector (P1: 5 Pin)

| <u>Pin No.</u> | Description |

|----------------|-------------|

| 1              | -12 V       |

| 2              | Unused      |

| 3              | GND         |

| 4              | +5 V        |

| 5              | +12 V       |

#### Table 4 Power Connector Configuration

#### 5.2 RS232C Connector (P2,3: 25 Pin)

| <u>Pin No.</u>         | Description (DCE P3)                                                                                          |  |

|------------------------|---------------------------------------------------------------------------------------------------------------|--|

| 1<br>2<br>3            | Frame Ground<br>Transmit Data (Receive Data P3)<br>Receive Data (Transmit Data P3)                            |  |

| 4<br>5<br>7<br>8<br>20 | Request to Send<br>Clear to Send<br>Signal Ground<br>Data Carrier Detect<br>Data Terminal Ready (Printer Busy |  |

Polarity of Data Signals: - True Polarity of Control Signals: + True

Table 5 RS232C Connector Configuration

#### 5.3 Floppy Disk Controller Connector

| <u>Pin No.</u> | Description                                               |

|----------------|-----------------------------------------------------------|

| 6              | -Drive Select 3                                           |

| 8              | -Index/Sector                                             |

| 10             | -Drive Select 0                                           |

| 12             | -Drive Select 1                                           |

| 14             | -Drive Select 2                                           |

| 16             | -Motor On                                                 |

| 18             | -Direction Select: - Toward Center<br>+ Off Center        |

| 20             | -Step                                                     |

| 22             | -Composite Write Data                                     |

| 24             | -Write Enable                                             |

| 26             | -Track 00                                                 |

| 28             | -Write Protected                                          |

| 30             | -Composite Read Data                                      |

| 32             | -Side 1 Select (Ignored by one side<br>floppy disk drive) |

Pin 1, 2, 3, 4, and 34 are not used. All other odd number pins are grounded.

Table 6. FDC Connector Configuration

| <u>P</u> : | in No.                        | Description                   |

|------------|-------------------------------|-------------------------------|

|            | 1                             | WDAL 0                        |

|            | 3                             | WDAL 1                        |

|            | 5                             | WDAL 2                        |

|            | <b>7</b>                      | WDAL 3                        |

|            | 9                             | WDAL 4                        |

|            | 11                            | WDAL 5                        |

|            | 13                            | WDAL 6                        |

|            | 15                            | WDAL 7                        |

|            | 17                            | WA O                          |

|            | 19                            | WA 1                          |

|            | 21                            | WA 2                          |

|            | 23                            | -WCS (Winchester Chip Select) |

|            | <b>25 1 1 1 1 1 1 1 1 1 1</b> | -WWE (Winchester Read Enable) |

|            | 27                            | -WWAIT                        |

|            | 29                            | WINTRQ (Interrupt Request)    |

|            | 35                            | WDRQ (Data Request)           |

|            | 37                            | -WMR (Master Reset)           |

|            | 39                            |                               |

Pin 31, 33 are not used. All even number pins are grounded.

Table 7. WDC Connector Configuration

#### 5.5 Centronics-type Printer Interface Connector (P4: 40 Pin)

40 pin right angle header is used on the board, so the pin configuration on the board is different from the 36 pin connector on the rear panel but it will be matched when they are connected together.

Refer to Figure 18 for comparison of two connector pin assignment between 40 pin connector on the board and 36 pin connector on the rear panel which will be hooked up to the printer.

Table 8 describes the pin configuration of the connector on the board.

| CONNECTOR ON THI | BOARD | CONNEC | TOR ON | THE REAR | PANN | IEL |

|------------------|-------|--------|--------|----------|------|-----|

| 39 37            | 5 3 1 | 18 17  |        | 3        | 2    | 1   |

| 40 38            | 6 4 2 | 36 35  | ,<br>  | 21       | 20   | 19  |

Figure 18. Comparison of Two Connectors for Printer

| <u>Pin No</u>                                                                                                                                        | n de la contra de l<br>■<br>■ tra de la contra d |                                                                                                                  |                                      | Description                                                                                                                                                                                      |                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Rear Panel<br>Connector                                                                                                                              | Board Po                                                                                                                                                                                                                               | ort/Data Bi                                                                                                      | t                                    |                                                                                                                                                                                                  |                                                                                                                                             |

| 1, 19*<br>2, 20<br>3, 21*<br>4, 22*<br>5, 23*<br>6, 24*<br>7, 25*<br>8, 26*<br>9, 27*<br>10, 28*<br>11, 29*<br>12<br>13<br>31, 30*<br>14<br>32<br>15 | 1, 2*<br>3, 4*<br>5, 6*<br>7, 8*<br>9, 10*<br>11, 12*<br>13, 14*<br>15, 16*<br>17, 18*<br>19, 20*<br>21, 22*<br>23<br>25<br>26, 24* (W6)<br>27<br>28<br>29                                                                             | DØ/Ø<br>D1/Ø<br>D1/1<br>D1/2<br>D1/3<br>D1/4<br>D1/5<br>D1/6<br>D1/7<br>BSTB/P10<br>DØ/5<br>DØ/4<br>DØ/6<br>DØ/1 | (W5)<br>(W4)<br>(W8)<br>(W7)<br>(W3) | -Data strobe<br>Data 0<br>Data 1<br>Data 2<br>Data 3<br>Data 4<br>Data 5<br>Data 6<br>Data 7<br>-Ackn1g<br>Busy<br>** PE (paper emp<br>*** Select<br>-Input Prime<br>Gnd<br>*** -Fault<br>Unused | Output<br>Output<br>Output<br>Output<br>Output<br>Output<br>Output<br>Output<br>Input<br>Input<br>Input<br>Input<br>Input<br>Input<br>Input |

| 33<br>16                                                                                                                                             | 30<br>31                                                                                                                                                                                                                               | DØ/2                                                                                                             | (W2)                                 | **Light Detect<br>GND                                                                                                                                                                            | Input                                                                                                                                       |

| 34<br>17<br>35<br>18<br>36                                                                                                                           | 32<br>33<br>34<br>35<br>36                                                                                                                                                                                                             | DØ/7                                                                                                             | (W9)                                 | LC Pulse<br>Gnd<br>Unused<br>Unused<br>Unused                                                                                                                                                    | Output                                                                                                                                      |

\* Second pin number indicates return ground.

Pin 37, 38, 39, and 40 are not connected.

\*\*Ground if no connection

\*\*\*Tie high if no connection

Table 8: Configuration of parallel Printer Interface

#### 5.6 User system connector: RS422 (P7: 15 pin, P8-P12: 16 pin)

There are two types of connectors for RS422 on the system board. User 1 connector is D type 15 pin (P7) but from user 2 to user 6 (P8 to P12) connectors are 16 pin header type but these are connected to the D type on the rear panel eventually. The difference is only due to the different numbering order between those two types. Refer to Figure 19 for comparison.

| D Type                             | Header | Туре               |

|------------------------------------|--------|--------------------|

| 8 7 6 5 4 3 2<br>15 14 13 12 11 10 | <br>   | 7 5 3 1<br>8 6 4 2 |

Figure 19 Two Different Type Connector Pin Order for RS422

a. P7 (D type: 15 Pin)

| Pin No. | Description | Pin No. | Description                                                |

|---------|-------------|---------|------------------------------------------------------------|

|         |             |         |                                                            |

|         |             |         | $(e_{k+1}, e_{k+1}) \in \mathbb{R}^{n} \to \mathbb{R}^{n}$ |

| 1       | Shield      | 9       | -TXD                                                       |

| 2       | TXD         | 10      | -RXD                                                       |

| 3       | RXD         | 11      | -RTS                                                       |

| 4       | RTS         | 12      | -CTS                                                       |

| 5       | CTS         | 13      | TXC                                                        |

| 6       | -TXC        | 14      | RXC                                                        |

| 7       | -RXC        | 15      | Reserved for<br>Manufacturer                               |

| 8       | Signal GND  |         |                                                            |

Table 9. D Type Configuration for RS422

## b. P8 to P12 (header type: 16 pin)

| <u>Pin No</u> | · .   | Description |              |       | Description |

|---------------|-------|-------------|--------------|-------|-------------|

| "D"<br>Conn.  | Board |             | "D"<br>Conn. | Board |             |

| 1             | 1     | Shield      | 9            | 2     | -TXD        |

| 2             | 3     | TXD         | 10           | 4     | -RXD        |

| 3             | 5     | RXD         | 11           | 6     | -RTS        |

| 4             | 7     | RTS         | 12           | 8     | -CTS        |

| 5             | 9     | CTS         | 13           | 10    | TXC         |

| 6             | 11    | -TXC        | 14           | 12    | RXC         |

| 7             | 13    | -RXC        | 15           | 14    | Unused      |

| 8             | 15    | Signal GND  | N/C          | 16    | Unused      |

Table 10. Header Type Configuration for RS422

5.7 Reset Power On Light Connector (P6: 3 Pin)

| <u>Pin No.</u> | Description              |

|----------------|--------------------------|

| 1              | GND                      |

| 2              | Reset SW (normally high) |

| 3              | Reset SW (normally low)  |

Table 11. Reset, Power On Light Connector Configuration

5.8 LED Description

4 LED's are used for diagnostic purposes. They are lit when the data line goes low. The corresponding port address is 00 the data byte assigned to each LED is as follows.

| LED No. | Data Byte |

|---------|-----------|

| 1       | FO        |

| 2       | F1        |

| 3       | F2        |

| 4       | F3        |

The LED sequence for each test is as follows:

| Lit LED       | Test In Process           |

|---------------|---------------------------|

| 0 0 0 🕊 1     | MEM Test                  |

| o o 🕊 o 2     | DMA                       |

| o 🍟 o o 3     | WDC                       |

| Ψοοο4         | SIO                       |

| o o 📽 📽 1, 2  | PIO                       |

| ₩₩003,4       | FDC                       |

| ₩₩₩1, 2, 3, 4 | After finishing all tests |

### 6.0 Description for Jumpers

| <ul> <li>W1: 1) Connect B and C when used with service terminal.</li> <li>2) Connect A and B when used without service terminal.</li> </ul> |                                                                  |                                                                     |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------|--|--|

| W2-W9:                                                                                                                                      | Use as follows depending on th                                   | ne type of printer.                                                 |  |  |

| Jumper                                                                                                                                      | Related Signal and Pin No.<br>(Centronics-type) on rear<br>panel | Description                                                         |  |  |

| W2                                                                                                                                          | Light detect (pin 33)                                            | Connect when the printer<br>interface does not need<br>this signal. |  |  |

| W3                                                                                                                                          | -Fault (pin 32)                                                  | Connect when the printer<br>interface does not need<br>this signal. |  |  |

| W4                                                                                                                                          | Select (pin 13)                                                  | Connect when the printer<br>interface does not need<br>this signal. |  |  |

| W5                                                                                                                                          | Paper empty (pin 12)                                             | Connect when the printer<br>interface does not need<br>this signal. |  |  |

| W6                                                                                                                                          | -Input prime return (pin 30)                                     | Connect if GND is needed.                                           |  |  |

| W7                                                                                                                                          | GND (pin 14)                                                     | Connect if GND is needed.                                           |  |  |

| W8                                                                                                                                          | -Input prime (pin 31)                                            | Connect when the printer interface needs this signal.               |  |  |

| W9                                                                                                                                          | LC pulse (pin 34)                                                | Connect when the printer interface needs this signal.               |  |  |

7.0 POWER REQUIREMENTS

|      | Sys. Bd    | WDC        | Hard Disk  | Floppy Disk |

|------|------------|------------|------------|-------------|

| +5V  | 5.5 A Max. | 2.5 A Max. | l.0 A Max  | 0.5 A Max.  |

|      | 2.5 A Typ. | 2.1 A Typ. | .75 A Typ. | 0.45A Typ.  |

| +12V | 80 mA Max. |            | 5.0 A Max. | 2.2 A Max.  |

|      | 50 mA Typ. |            | 1.5 A Typ. | 0.8 A Typ.  |

|      |            |            |            |             |

| -12V | 50 mA Max. | 50 mA Max. |            |             |

|      | 30 mA Typ. | 25 mA Typ. |            |             |

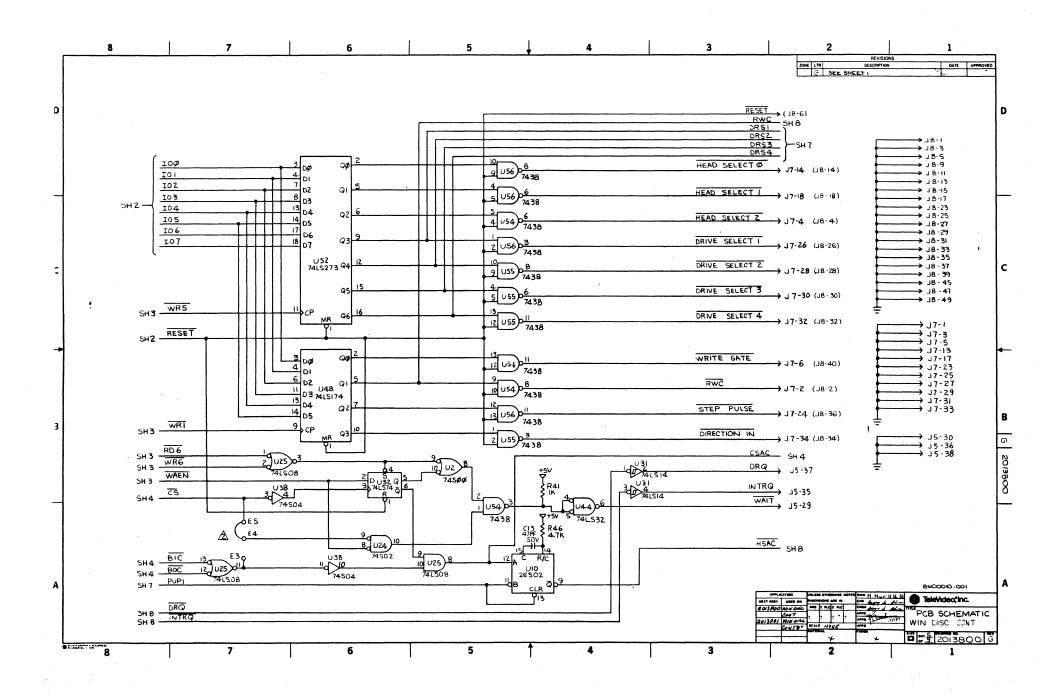

#### 8.0 WINCHESTER DISK CONTROLLER

#### 8.1 Overview

The WD1000 hard disk controller is a discrete implementation of all the functions required to control SA1000/ST506-compatible Winchester (hard) disk drives via a standard data and control BUS. The controller is fabricated using a mix of high-speed bipolar and NMOS devices contained on a single, two-sided PC board.

The design of the circuitry makes use of a high-speed Microcontroller called the 8X300, newly developed NMOS support devices, Schottky devices, and low power Schottky devices. Together they work to achieve low component count and cost while maintaining high performance and reliability.

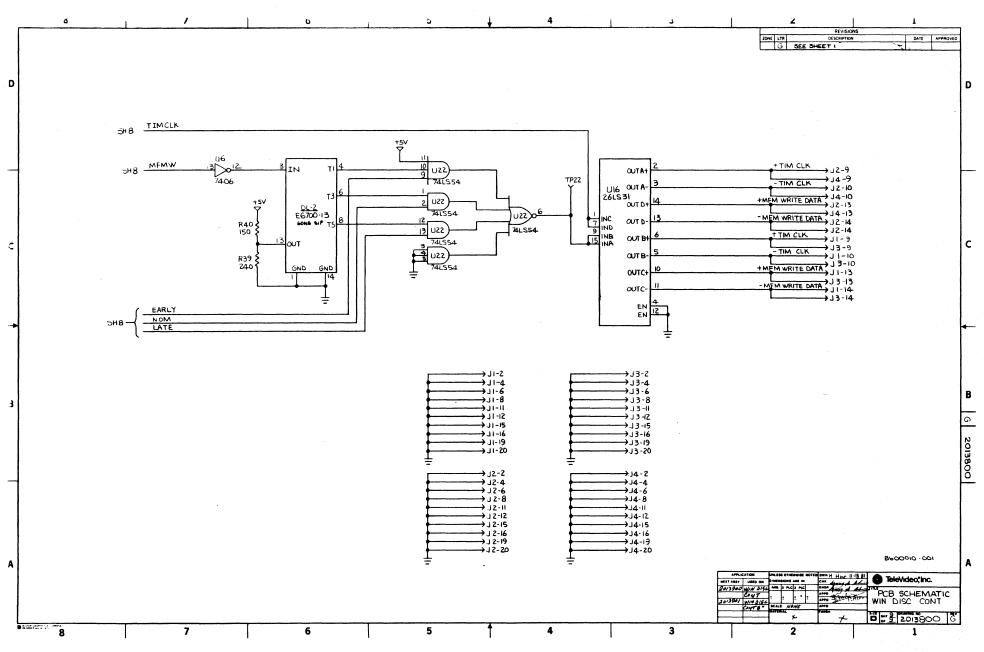

All I/O connections are made using standard ribbon cable connectors. Standard pin-out configurations for disk interface connectors are provided to permit direct pin-for-pin connection to ST506 compatible 5" drives.

All power for the board can be supplied from a single 5-volt power supply on a separate connector.

All host-to-disk data transfers are buffered by onboard RAM to achieve totally asynchronous transfers to and from the disk by the host.

The disk controller is built around five basic sections:

- 1. Processor functions

- 2. Serial data separation

- 3. Data conversion and checking

- 4. Serial data generation

- 5. Host interface functions

#### 8.2 Processor Functions

All functions of the WD1000 controller are ultimately controlled by the onboard processor. Due to the high data rates associated with hard disk drives, processing of data and control of machine functions within the circuitry requires a processor capable of extremely fast execution speed. The processor used is the 8X300, a bipolar microcontroller particularily well suited for handling data efficiently at high rates.

The 8X300 operates at a basic clock rate of 8 MHz and performs all operations within 2 clock cycles giving it a speed of 4 MIPS (Million Instructions Per Second) or one instruction executed every 250 nS. The architecture of the processor is different from most other microprocessors in that no common data or address BUS is provided to be shared by RAM, ROM or peripheral devices.

Instructions are fetched from ROM via a dedicated instruction address and data BUS. The instruction address BUS (IAO-IA13) is capable of directly accessing 8K words of program storage. However, the WD1000 uses only the first 10 address lines, limiting onboard program storage to 1K words.

Program data is input to the 8X300 (U50) on the Instruction Data Operation. All BUS designations utilized by the 8X300 are reversed from the traditional LSB to MSB weighting. These bus lines have all been renamed on the schematic of the WD1000 to provide a more conventional designation system for the board.

#### 8.2.1 Fast I/O Select

An extension byte has been added onto the instruction data memory to provide port access decoding on an instruction-by-instruction basis. This "Fast I/O Select" byte is not processed by the 8X300. It is decoded by auxiliary hardware to provide eight read strobes and eight write strobes which route data to the various devices distributed along the interface vector BUS.

The Fast I/O byte is latched into a 6-bit latch (U27) on the trailing edge of MCLK to ensure the data remains stable during the entire instruction. This data selects a read strobe and write strobe through two 1-of-8 decoders (U20 and U26) which are alternately enabled by the -WC control strobe produced by the 8X300. To provide edges on read strobes during sequential read operations from various ports, the red strobe decoder (U20) is always disqualified at the end of instruction by +MCLK' which is a delayed copy of +MCLK. This delay compensates for timing races through the Fast I/O latch (U27) and the control signals.

Because each decoder has a unique input, it is possible to select any read port with any write port during each instruction. Data is transferred between the processor and its ports on a separate 8-bit BUS called the "I/O" BUS. This BUS is active low. It must be noted that this BUS is in no way related to the instruction data BUS and can be thought of as simply an 8-bit bidirectional I/O BUS of the 8X300. In fact it has been renamed as I/O0-I/O7 to reflect this distinction.

#### 8.2.2 Internal BUS Control

Several BUS control signals are produced by the 8X300 to identify and strobe the data in the I/O BUS. WC (write control) is a signal which determines the direction of the data to and from peripherals. When WC is false (during the first half cycle), data is being input to the 8X300 from the I/O BUS. When WC is true (during the second half cycle), data is being output from the 8X300 onto the I/O BUS. SC (select control) is a signal which becomes active during the second half cycle instead of WC if the I/O BUS contains an 8-bit I/O address. In the WD1000, both WC and SC are combined by a NOR gate (U24) to indicate all accesses to any port. This arrangement allows 8-bit immediate-data moves from the 8X300 to any output port within one instruction, instead of the normal 5-bit immediate moves provided for by the instructions set.

All instruction fetches occur late in the second cycle of the preceding instruction. This time is marked by the generation of a 65 nS (nominal) active high pulse called MCLK which occurs every instruction. MCLK is used to latch data prior to being input on the I/O BUS to insure stability during reads. It is also used to disqualify any read strobes that would otherwise remain true during the second clock cycle of any instruction which does not write to a port.

Two additional BUS control signals are produced by the 8X300. They are RIGHT BANK SELECT (-RB) and LEFT BANK SELECT (-LB). These are not used, however, in the WD1000 due to the implementation of the Fast I/O Select logic.

#### 8.2.3 Reset Circuit

The 8X300 is held in reset for approximately 40 mS after initial power on. This is accomplished by an RC network (R42, C68 and CR3) which drives a Schmitt trigger (U31) to provide a proper rise/fall time on the -RESET line of the 8X300. Alternate reset of the processor can be accomplished by dropping -MR (J5 pin 39) whenever the host wishes to reset the controller. A Schmitt trigger (U31) is provided with a 4.7K pull-up (R43) to buffer the -MR input from the host. -RESET also propagates to the drive control latches (U52 and U48) and their associated line drivers (U54-56) and host interface WAIT (U320, DRQ and INTRQ latches (U30), ensuring proper initialization of these functions during power-up and subsequent resets from the host.

## 8.2.4 Processor Power Supply

Power is supplied to the 8X300 from the +5 Volt (Vcc) power BUS. Due to the internal operation of the 8X300, an on-chip voltage reference is provided to produce bias to an external pass transistor (Q4). This drops Vcc to the 8X300 to approximately +3.0 Volts. All signals into and out of the 8X300 are internally level shifted to be TTL compatible.

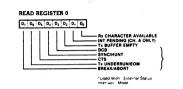

## 8.2.5 Read and Write Ports

Throughout the circuit, output ports are formed by D type latches using write strobes (WRO-7) to latch data into the ports. Reading of ports is universally accomplished by using read strobes (RDO, RD2, RD4-6) that enable selected tri-state output devices on the I/O BUS. Additionally, two read strobes are used to clock the host DRQ and INTRQ latches (U30) and one read strobe is left unused as a "dummy" port for instructions not requiring data from a port. This insures troublefree operation of the Fast I/O port decoders.

## 8.2.6 Read/Write Memory

Since the 8X300 does not permit data to be saved or retrieved from dedicated program storage, RAM must be installed on the I/O BUS. RAM must, therefore, be accessed via the I/O BUS by I/O instructions like all other port accesses. To provide for addressing the RAM, three latch counters (U40, 45 and 46) are connected to the I/O BUS to receive and store addresses required to access the RAM (U33 and U39).

## 8.2.6.1 RAM Addressing

The RAM address BUS (RAO-RA9) uniquely addresses 1 of 1024 memory locations. As each counter chip reaches a count of 0, it sets a borrow condition to the next higher counter which is decremented at the end of the next access to RAM. When all bits of the address have been reset, the -ROVF bit on the last counter (U40) is reset providing an overflow status which can be read by the processor on U43. By setting various beginning address values, -ROVF can be used to mark the end of any RAM access loop from 1 to 1024 bytes in length. In the WD1000, this function is used for setting sector buffer lengths of 128, 256, or 512 bytes.

## 8.2.6.2 Sector Buffering

All data read from the disk or written to the disk is passed through the RAM to provide buffering required for asynchronous data transfer between the host and disk. The counters are postdecremented which means that effective addresses are stable to the RAM by at least the instruction prior to the actual access. This preselection feature effectively reduces RAM access time to the output enable and propagation time of the RAM for read operations and the width of the minimum -WR strobe pulse for write operations.

## 8.2.6.3 RAM Accessing

RAM access is initiated by -RCS which is the logical OR (by U25) of -RDO and -WRO generated by the Fast I/O decoders (U20 and U26). Data to be read from RAM will be placed on the I/O BUS whenever -RCS is low and -WC is high. Data is written into a selected RAM cell on the trailing edge of -WC if -RCS is low. During writes, both -WC and -RCS will be low for at least 120 nS so that data setup time requirements are met.

## 8.2.6.4 Scratchpad Operations

Because the RAM address counters can be preset, direct reads and writes to a specific address are possible. This function is used for scratchpad storage during program execution. This mode of RAM access requires 2 or 3 instruction cycles for each random access to the RAM as opposed to 1 for sequential access using the

#### post-decrement feature.

## 8.2.7 MAC Control Port

Basic control of the various functional sections of the WD1000 is accomplished by a dedicated 6-bit control port called MAC CNTRL (U34). MAC CNTRL enables the functions of the WAIT control circuitry (-WAEN), CRC generation (-CRCIZ), gating of read data into data separation circuitry (RGATE), selection of read or write functions (-WRITE), control of CRC check word output (-IBLA) and AM detection (SRCH). MAC CNTRL output states are latched into the port by a write strobe (WR7). Additionally, any time MAC CNTRL is loaded with a new byte, the lower two data bits (I/O0-1) are strobed into the upper two address counter/latch bits (RA8,9).

All remaining ports are distributed among the basic functional sections of the WD1000 and are described in detail within the discussion of those functions.

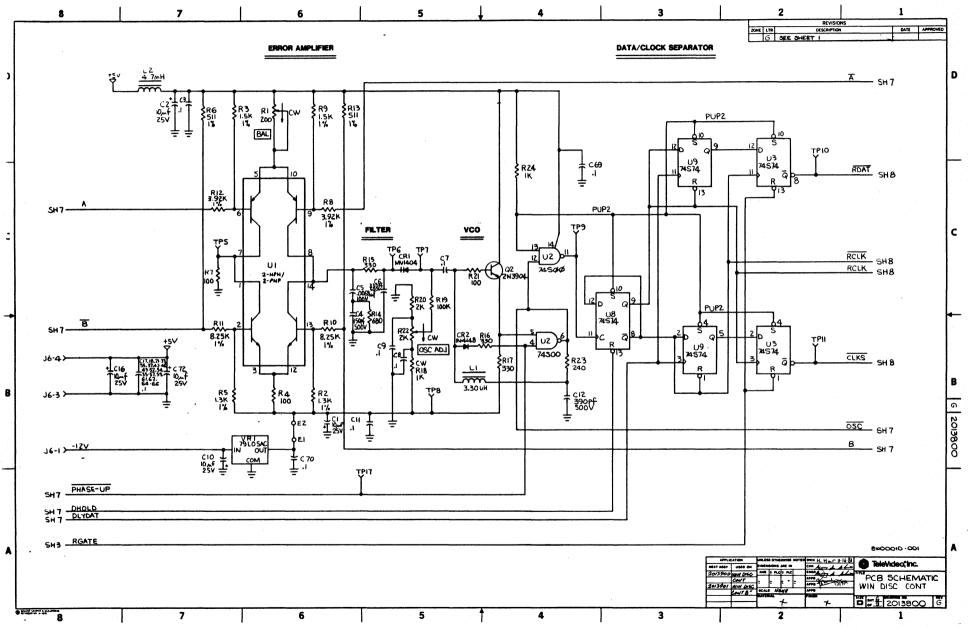

8.3 Serial Data Separation

The WD1000 controller contains on-board circuitry to process incoming MFM data from the drive by a process called data separation. Here, some background information may be helpful:

In order to provide maximum data-recording density for maximum storage efficiency, data is recorded on the disk using a Modified Frequency Modulation (MFM) technique. This technique requires clock bits to be recorded only when two successive data bits are missing in the serial data stream. This reduces the total number of bits required to record a given amount of information on the disk. This results in an effective doubling of the amount of data capacity, hence the term "double density".

The fact that clock bits are not recorded with every data bit cell requires circuitry that can remain in sync with data during the absence of clock bits. Synchronous decoding of MFM data streams requires the decoder circuitry to synthesize clock bit timing when clocks are missing and synchronize to clock bits when they are present. This is accomplished by using a phase-locked oscillator employing an error amplifier/filter to sync onto and hold a specific phase relationship to the data and clock bits in the data stream. The synthesized clock called RCLK can then be used to separate data bits from clock bits and to shift the resultant serial data into registers for parallelization into bytes.

## 8.3.1 Incoming Data Selection

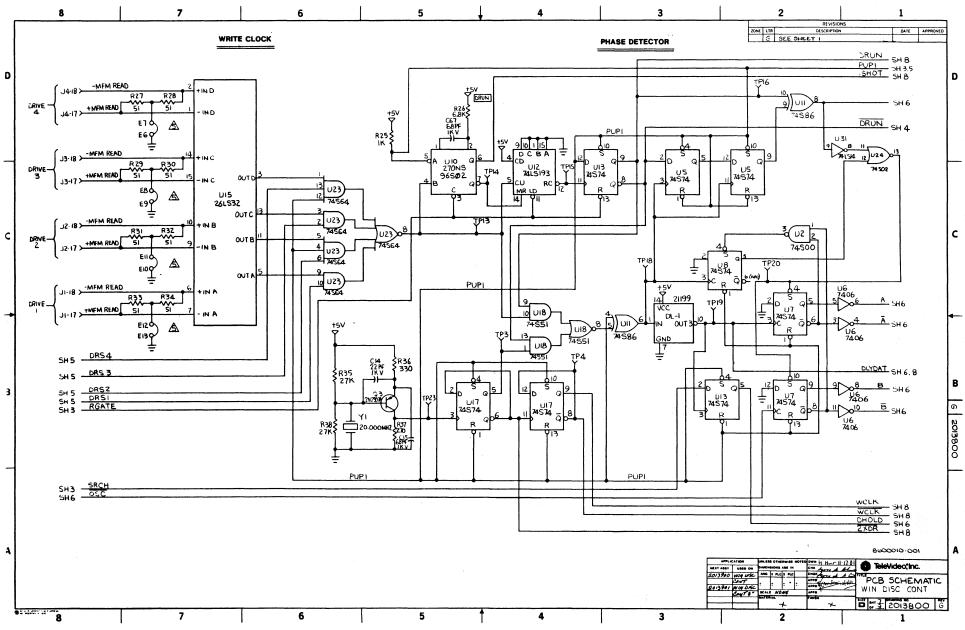

In the WD1000, serial data is input from up to four radiallyconnected drives via a quad RS 422 differential receiver (U15). The receiver converts differential input data to TTL levels for use by the controller. The data from the selected drive is then routed to the data separation circuitry by a four-section AND/OR/INVERT gate (U23). At this point data and clocks are still combined and appear as 50 nS (nominal) active high pulses spaced at intervals of 1, 1.5, or 2 times the RCLK period. This data is presented to the input of another AND/OR/INVERT gate (U18) which will gate either MFM data or a reference clock into the first stage of the VCO error amplifier circuitry.

## 8.3.2 Reference Clock

The reference clock is derived from the write clock crystal oscillator (Q3, U17 and associated circuitry). This oscillator uses a fundamental crystal cut to oscillate at 4 times the RCLK frequency. The 4X output is then divided by U17 to produce both a 2X clock (2XDR) which is used as a reference and a 1X clock (WCLK) which is used to produce MFM write data for the disk. The crystal (Y1) frequency is 20.000 MHz for ST506 compatible drives or 17.360 MHz for SA1000 compatible drives.

#### 8.3.3 Clock Gating

The gating of the reference and MFM data into the data separator is dependent on the condition of the read gate (RGATE) signal and the spacing of the data on the serial stream after RGATE is brought true. The techniques used to separate data from clocks make it necessary to run the VCO at a rate twice the data clock (RCLK) rate. The VCO is therefore set to an open loop frequency of 2X RCLK. Any variations in this rate due to variations in disk rotational speed must be compensated for by the VCO. Instantaneous shifts in data due to the effects of adjacent bit cells on the disk and minor noise must be ignored. Also, the response of the VCO must be adjusted to effectively override missing clock bits which occur as a result of the MFM recording technique.

The resultant compromise between response and reject requirements of the VCO causes the VCO to have a tendency to become locked onto harmonics of the data rate rather easily. This is likely to occur if the VCO is connected to a data stream over a field of data which has data bits spaced at 1.5 or 2 times the actual RCLK time intervals.

To prevent this from occurring, the VCO is always held locked onto a stable clock running at 2 X RCLK frequency whenever the controller is not actually reading data. Read data is switched to the VCO error detector only when it is known that the data stream frequency is equal to the RCLK frequency. This can occur only when the data is a solid stream of all ones or all zeros.

#### 8.3.4 High Frequency Detector

The switching function is initiated immediately after the RGATE goes true. It will only switch read data into the VCO after 16 consecutive ones or zeros (high frequency) are detected by a one-shot (U10) and counter (U12) connected directly to the raw MFM data.

The one-shot is adjusted for a pulse width of 1.25 times the RCLK period. This is a 250 +/-10 nS for ST506 compatible drives and 287 +/-10 nS for SA1000 compatible drives. These adjustments of the DRUN one-shot (U10) provide tolerance of up to 1/4 RCLK period in jitter on the MFM data bits while still being able to distinguish MFM zeros or ones from other data patterns.

Each clock or data bit on the serial stream triggers the oneshot. If the time between successive triggers is less than the one-shot time constant, the one-shot remains retriggered.

As the one-shot is triggered by data stream bits, so is the up/down counter (U12), whose count mode is controlled by the state of the one-shot outputs. While the one-shot is being retriggered, the counter counts up.

When any data bit fails to reach the one-shot before its time constant is over, the one-shot resets and in turn clears the counter. Only when 16 successive retriggers occur can the counter reach its terminal count. At this time, the counter overflow goes true and sets up the -DRUN latch output (U13 pin 8) low which switches read data in and reference clock out. An AND/OR/INVERT gate (U18) performs the switching. -DRUN is read through U42 by the 8X300 to determine the condition of the MFM data stream.

The data and clocks are now connected to the first stage of the data separator. The heart of the data separator is the VCO (U2 and associated circuitry) and the error amplifier and filter (U1). As previously stated, the VCO runs at a frequency twice that of the RCLK rate.

## 8.3.5 VCO

RCLK is produced by the VCO through a divide-by-two counter (U8). The VCO is a discrete LC oscillator with a shunt capacitor formed by a hyper-abrupt tuning diode (CR1). The diode varies its capacitance in accordance with the amount of reverse DC bias applied to its PN junction. As the bias decreases, the capacitance increases, pulling the oscillator down in frequency. Conversely, as the bias increases, the oscillator frequency rises.

The VCO performs conventionally with one exception. To help the VCO lock onto the incoming signals more quickly, an external timing signal freezes the output of the VCO in the high state. This is done by disqualifying U2 in the VCO feedback circuit and by removing bias from the transistor (Q2) which provides loop gain in the oscillator. -PHASEUP performs this function and is present just after the switch over from reference clock to MFM data is made.

The width of -PHASEUP is directly related to the difference in timing between the positive going transition of the VCO output and the positive transition of the second data/clock bit of the MFM data stream. -PHASEUP causes the output of the VCO to rise in phase with the MFM data from the drive. This allows the VCO to adjust its phase slightly to center data/clocks within the RCLK rather than performing a frequency acquisition to lock onto the data stream. The phase acquisition is much faster and easier to achieve and results in vastly improved performance.

#### 8.3.6 Error Amplifier

The error amplifier and filter control the VCO. The error amplifier is a balanced differential amplifier whose output either sources or sinks current to the filter stage. The error amplifier output is pulse-width modulated by the phase detector (U6, 7).

Whenever the VCO is running too slow, the error amplifier receives pulses from data bits before pulses from the VCO clock. This causes the error amplifier to produce pump-up pulses to the filter. The filter integrates these pulses producing an average increase in the voltage to the cathode of the hyper-abrupt tuning diode (CR1). This effectively increases the reverse bias on the diode which reduces its capacitance and therefore increases the VCO frequency slightly to match the phase of the incoming data.

Whenever the VCO is running too fast, the error amplifier produces pump-down pulses to the filter. The diode then receives decreased reverse bias, more capacitance, and lower VCO frequency.

The operating point of the tuning diode (CR1) is initially set for an open loop VCO frequency of two times RCLK by setting -OSC ADJUST and monitoring the VCO output. This adjustment places the initial bias through the bias divider (R18-20, R22 and C8-9) at approximately -2.8 V to -3.2 V. At this setting the most responsive region of the diode is being used giving higher gain in the VCO. To keep the initial bias voltage close to three volts with varying disk data rates, the VCO inductor (L1) is 3.3 UH for 5 MHz drives and 3.9 UH for 4.34 MHz drives.

The VCO is forced to match the phase of the incoming data. Once the VCO is close to the phase of the incoming data, the pump pulses become very small or are missing completely. It must be noted, however, that a slight error is always be present because, without pumps, the filter floats and the VCO drifts. The overall gain of the error amplifier and the VCO maintains this very small error, resulting in very close tracking between the VCO ouput phase and the incoming data phase.

As previously stated, great care is taken to insure that the VCO starts on the same phase as the incoming data. If this were not the case, the error amplifier would produce very large pumps in an attempt to pull the VCO onto frequency and phase. Due to the gain of the error amplifier and the required characteristics of the filter, the integrated pump pulses would over-compensate, causing the VCO to overshoot in its attempt to lock-on. This

action would continue in a diminishing fashion until lock-on occurred. Unfortunately, the data sync fields it was trying to acquire would be over by the time the VCO finally acquired lockon. -PHASEUP is, therefore, extremely important to the overall ability of the data separator to function reliably.

## 8.3.7 Sample on Phase Detector

The circuitry which feeds the error amplifier is called the Sample on Phase Detector. This circuit consists of several D latches (U7) and a delay line (DL1). The function of the circuit is to provide time windows during which the leading edges of the incoming MFM data can be compared to the leading edges of the VCO clock. These windows are approximately 50 nS in length. The windows are initiated by a leading edge of any data bit as it enters the detector. They are terminated by that same data bit, edge-delayed by a net 50 nS (60 nS in the delay line minus approximately 10 nS in propagation delays).

When both the delayed data bit and the nearest VCO edge arrive at the detector, the detector is reset until the next data bit arrives on the MFM data stream. The delayed data bit sets its half of the detector latches to produce a pump-up condition at the error amplifier. The VCO clock edge sets its half of the detector to produce a pump-down condition. When the circuit is balanced, either both pumps are on or both pumps are off, producing no net pump-up or down.

#### 8.3.8 Window Extension

Once the VCO has been locked onto the phase of the incoming data, the actual separation of data and clocks can occur. This is done by using a technique called window extention. This technique causes data bits to first have their leading edges shifted into the center of the RCLK half cycles and then to be latched or extended until the next rising edge of the RCLK. The shift is accomplished by tapping the data off the sample on-phase detector delay line at the 60 nS tap and inverting the VCO clock to the RCLK divider (U8). The delayed data clocks a pair of latches (U9). The 'data' latch has its D input and CLEAR connected to +RCLK and the 'clock' latch has its D input and CLEAR connected to -RCLK.

If an MFM data bit enters the latches while -RCLK is high, it will be extended as a data bit. If -RCLK is high, it will be extended as a clock bit. Due to this extension technique, bits can jitter approximately 1/4 the RCLK period without being lost. The output of each latch is then further extended by feeding directly into another stage of latches (U3) and clocked on alternate edges of RCLK. The final outputs of the data extension/separation stage are two separate signals, one consisting solely of NRZ data, and the other NRZ clocks. NRZ data and clocks are finally in a form suitable for processing by subsequent circuitry within the WD1000.

## 8.3.9 Clock Detection

Due to the nature of MFM data encoding, it is impossible to know exactly if MFM bits are data or clocks. This ambiguity results in having to create circuitry to assume that bits on -RCLK are actually data bits until the VCO is locked on and a unique data/clock pattern is detected. This is accomplished by holding the VCO to RCLK divider (U8) reset until it is fairly certain that bits on the data stream are actually clocks belonging to a field of zero data.

Once this assessment has been made, the processor releases the AM detector (U14) by raising the SEARCH signal. This signal releases a latch (U13) which removes -DHOLD from the RCLK divider (U8) on the next rising edge of a MFM data bit so that CLOCKS will be on the -RCLK phase and DATA will be on the +RCLK phase. The processor makes its assessment of the state of the data stream solely on the occurrence of a significant run of zeros which are detected by the one-shot (U10) in the DRUN circuit. Once released, the phase of RCLK vs data and clocks remains stable throughout the read of an ID field or data field. Whenever SEARCH is dropped, the VCO to RCLK divider is once again reset and no RCLKS are produced.

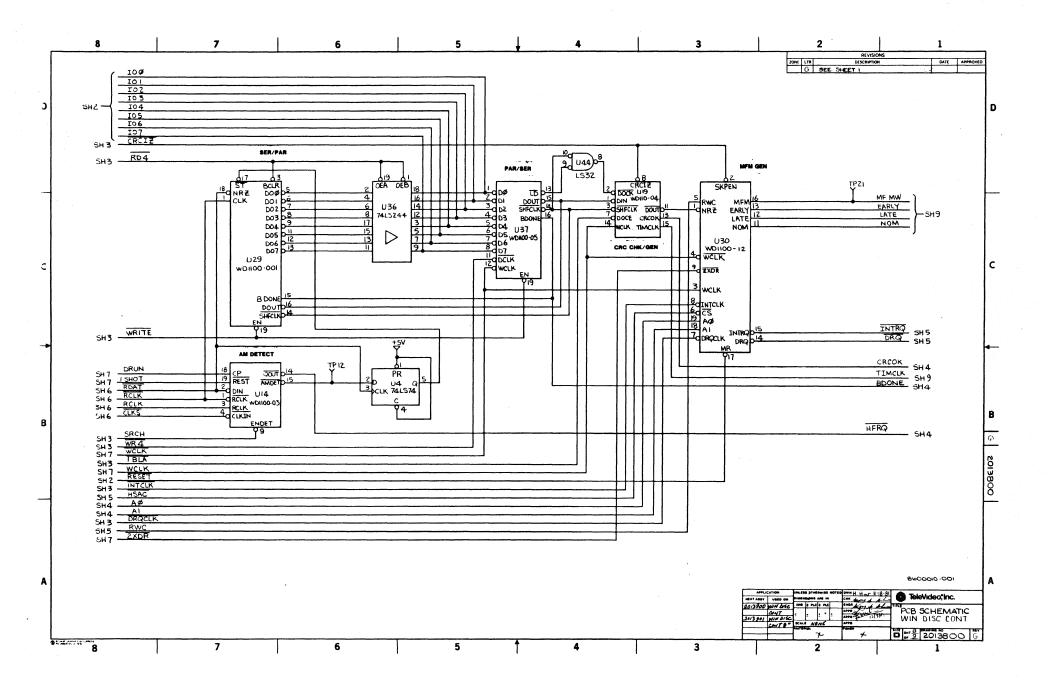

## 8.4 Data Conversion and Checking

MFM data which has been separated to form NRZ data and clocks is processed through specialized circuitry to prepare it for parallel processing by the 8X300. This processing consists of 3 functional circuits.

- 1) AM detection (U14)

- 2) Serial to parallel conversion (U29)

- 3) CRC checking circuit (U19)

Each function is discussed separately but many interdependencies exist.

## 8.4.1 AM Detection

As previously stated, it is impossible to know whether serial data bits are actually data or clock bits by just looking at the data stream. It is also impossible to determine byte boundaries. This problem is solved by a uniquely recorded data/clock pattern called an Address Mark (AM). The AM consists of a data pattern of HEX 'Al' with a missing clock pattern of HEX 'OA'. Normally, a data byte of HEX 'Al' requires a clocking pattern of HEX 'OE'. In fact, due to the rules of MFM data encoding, an alternating clock pattern such as HEX 'A' or HEX '5' cannot exist legally.

The AM is used to uniquely identify the start of a field of information (Data or ID field) within each sector. Preceding each AM on the disk there is always a long run of "zero" data. Zeros have a clock bit for every RCLK. When attempting to read information from the disk, the WD1000 first acquires phase lock over a field of zeros. After this acquisition is achieved, the processor releases the AM detector (U14) by raising the SEARCH control line (SRCH) on the MAC CNTRL port (U34). Because of the circuitry associated with the VCO to RCLK divider, the -RDAT output of the data separator (U3 pin 8) will be high and the -CLKS output (U3 pin 6) will be low. -RCLK will be the shifting clock for -RDAT and +RCLK will be the shifting clock for -CLKS. These 4 signals are routed into the AM detector.

Inside the AM detector, the -RDAT is shifted into an 8-bit synchronous serial shift register and clocked on the falling edge of -RCLK. -CLKS are shifted into a similar shift register on the falling edge of +RCLK. The output stage of the -RDAT register is dumped into an 'Al' comparator and the output stage of the -CLKS register is dumped into an 'OA' comparator. AM detection occurs when both detectors are true, thereby making the relationship between data and clocks known. It is also known that data is being clocked by -RCLK so -CLKS can actually be discarded; their only purpose was in detecting AM. The -AMDET signal is used as a synchronization signal to start subsequent conversion circuitry. The -AMDET signal remains true until the processor again deasserts the SEARCH control line.

8.4.2 Serial to Parallel Conversion

After an AM has been detected, the Serial to Parallel converter (U29) takes over. NRZ data and -RCLK are used to shift data bits into an 8-bit serial to parallel shift register. As each bit is shifted, a divide-by-8 counter circuit is incremented. After every eight bit of data is shifted, the counter produces an overflow pulse, marking byte boundaries in the serial data stream. The overflow bit from the counter resets the counter, clocks the data from the shift register into an 8-bit parallel latch, and sets a tri-state flag register called BDONE. The flac can be read by the processor to see if any converted data is ready to be read from the latches.

When the processor sees BDONE in the true state, it services the device by gating data onto the I/O BUS using read strobe 4 (RD4) in conjunction with a tri-state buffer (U36). The act of reading the latches also clears off the pending BDONE flag. As successive bytes are processed, the BDONE is serviced by the processor as data becomes available.

Outputs from the serial to parallel device also include -SHFTCLK and -DOUT. -SHFTCLK is actually -RCLK propagated through the device. -DOUT and -SHFTCLK are tri-stated along with BDONE, and are active only when -WRITE is high, indicating a read mode of operation. -DOUT and -SHFTCLK are routed to the CRC generator checker device.

8.4.3 CRC Checking Circuit

Data recorded on magnetic media is prone to several types of errors which could render data unusable if some form of error detection were not employed. On the WD1000, a Cyclic Redundancy Check (CRC) is performed on all data transfers from the disk. The CRC is an error detection code consisting of 16 additional bits which are appended to every ID field and data field on the disk. These bits are produced by dividing the data stream serially with a large polynomial. This division produces a unique 16-bit value for any information passed through the CRC generator.

As data is being read from the disk, the CRC generator recomputes the original CRC bits. After the last two bytes (containing the original recorded CRC) are read, the value in the CRC generator must always be zero. When this happens, the data was correctly read and the controller will not flag an error. If, however, the CRC generator is not zeroed after it has checked all bytes of the recorded data, then the controller will flag the data as erroneous and enter into a retry condition. If after attempting to correctly read the data 16 times, the controller still cannot get correct data, the read is aborted and the host is informed that the data in the buffer is questionable.

The WS1000 uses the same device to generate and check CRCs for data being written and read on the disk. The polynomial used is:

X16+X12+X5+1 (commonly called the CRC-CCITT polynomial)

During read operations, the processor polls the condition of the DRUN circuitry. When DRUN is true, it begins to search for an address mark. Once the AM is located, the processor starts to read parallel data which has been converted from NRZ data by the serial-to-parallel device. The processor terminates this activity when it has received the information it is looking for or if an error is detected.

While the processor is reading the parallel data, the CRC generator is reconstructing the CRC check value. The CRC generator is initialized by the processor setting -CRCIZ low for at least 250 nS during the search for the AM. -CRCIZ is originated on the MAC CNTRL port (U34). Upon receiving the -CRCIZ signal, the CRC generator/checker presets all 16 of its internal polynomial division shift registers to logic ones. It also arms an internal latch which enables the checking function on the leading edge of the first non-zero data to enter the device.

Prior to an AM there is a field of zeros (all data bits low), so the first non-zero data bit into the device will always be the most significant bit of the AM (HEX Al).

Once enabled by the first non-zero data bit, the CRC device shifts succeeding data bits into a feedback shift register string with exclusive OR gates tied to the feedback nodes on the first, fifth, twelvth and sixteenth registers. As each RCLK occurs, the registers divide the incoming data and a unique pattern of ones and zeros appear across the registers.

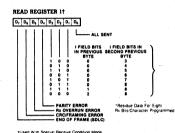

When the last bit of an ID or DATA field is processed, the pattern in the registers should be equivalent to the 16 bits appended to the fields during original recording. The appended bits are also entered into the CRC device. If all of the bits in the appended field are identical to the bits in the registers, then the exclusive OR gates in the register string will have flipped all of the ones to zeros and the CRC will have been satisfied.

The output of each register stage is tied to a 16-bit wide comparator which goes true when all of its inputs are zeros. The output of the comparator is retimed to remove any decoding slivers and is output as CRCOK. The processor can read CRCOK through U43 to see if a CRC error occurred.

After the CRC bits are processed, the data stream contains at least one more byte of zeros. It is the nature of the CRC polynomial that if no bits are set to ones in the registers, then none are flipped if a constant input of zeros is shifted into the registers. This provides a convenient latching function for the CRCOK flag which remains true for at least 1 byte after the last CRC check byte, giving the processor time to read the flag.

The data, clock and BDONE are supplied to the CRC device on a 3bit minibus. During read operations, the Serial-to-Parallel device (U29) sources these lines because the WRITE control line from MAC CNTRL (U34) is low. This enables the tri-state drivers on these lines. The Parallel-to-Serial device (U37) has its tristate drivers disabled.

#### 8.5 Serial Data Generation

The WD1000 records data on the disk in MFM format. To produce the proper data format, the WD1000 uses several specialized devices. These devices process the parallel data supplied by the host into a serial MFM data stream. The data supplied by the host is temporarily stored in the buffer RAM until the correct sector is located for the data to be written.

The process of writing is the opposite of reading except that the data separator circuitry is not required and the generation of the MFM data stream is produced by synchronous clocking techniques.

The functional sections of the serial data generation section are listed below:

- 1) Parallel to Serial conversion (U37)

- 2) CRC generation (U19)

- 3) MFM and precompensation (U30)

## 8.5.1 Parallel to Serial Conversion

Parallel data is converted into a serial NRZ data stream by the Parallel-to-Serial device (U37). The processor enables this conversion by lowering the -WRITE signal on MAC CNTRL (U34). -WRITE causes the tri-state buffers present on the parallel-toserial device to become active, supplying the CRC device with data, clocks, and BDONE strobes.

The processor presents parallel data on the I/O bus along with the -WR4 write strobe which latches the data into the parallel port on the trailing edge of the strobe. The write strobe also resets any pending BDONE. Inside the parallel-to-serial device, the parallel latches are loaded into a serial shift register on every eighth WCLK transistion. As the data is transferred to the shift registers, the BDONE status flag is set. The processor reads this flag through U43 to determine when to write the next parallel byte to the device. The timing of the parallel accesses is at a rate 1/8 that of the bit rate of the NRZ data stream. For ST506 compatible drives the byte timing is 1.6 us and for SA1000 drives it is 1.84 us.

The output of the last register in the shift string is brought out of the device as an NRZ serial data stream. The shifting clock is also brought out as SHFCLK to be used as the clock for the CRC device.

Whenever it is desired to write a repetitive string of identical data bytes, the processor can simply ignore the BDONE flag and permit the device to reload the data from its latches over and over again for as long as required to generate the field. This feature of the device is used in writing certain fields used in formatting.

## 8.5.2 CRC Generation

The CRC generator/checker (U19) is used to generate the CRC bits and to append them to the end of the data being written to the disk. This is the complementary function to that performed during reads. The operation of the polynomial generator is identical to read operations except that at the end of the data field, the processor sets a signal which causes the device to output the computed CRC after the data instead of reading the CRC and checking it.

The initial state of the shift registers within the device is forced to all ones by the processor pulsing -CRCIZ for approximately 250 nS while the parallel-to-serial device is outputting all zeros on the NRZ data line. At that time, a latch is set which holds the registers at ones until the first non-zero data bit enters the device. The first non-zero bit is the MSB of the AM (HEX Al) of the data field to be written. When the processor decides that enough zeros have been written to satisfy the sync field requirements, it stores a HEX Al in the parallelto-serial device. At the proper time (in sync with BDONE) the parallel-to-serial device begins to send the MSB of the AM to the CRC device. This starts the CRC polynomial generator and the CRC will be computed.