# MORROW DESIGNS $\Omega$

DISCUS M10--DISCUS M20--DISCUS M26

# WINCHESTER DISK SYSTEMS

# USER'S MANUAL

# Preliminary

| Intr | od:  | u c | t  | i   | on |    |    | 18  |     |   | 9 |   | 9 |   | w |   | 8 |   |     | 9  |   |    |       |    | 1  |

|------|------|-----|----|-----|----|----|----|-----|-----|---|---|---|---|---|---|---|---|---|-----|----|---|----|-------|----|----|

| The  |      |     |    |     |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    | de    | 9  | 3  |

|      | pl   |     |    |     |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    | 9     | 2  | 3  |

| Во   | ot   | st  | r  | aŗ  | )  | S  | 0  | f.  | tw  | a | r | е |   |   | 9 |   | 8 |   |     | w  |   | 20 | 10    |    | 4  |

| Syst |      |     |    |     |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    |       |    | 6  |

|      | 0    |     |    |     |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    |       |    | 7  |

|      | sta  |     |    |     |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    |       |    | 8  |

|      | 0    |     |    |     |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    |       |    | 8  |

| Prog | rai  | nm  | ii | n g | 5  | S  | p  | 9 ( | 2i  | f | i | C | a | t | i | 0 | n | S | so. | 20 | w |    | *     |    | 10 |

|      | e l  |     |    |     |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    |       |    | 10 |

| Di   | sk   | U   | t: | il  | i  | t  | У  | 5   | 3 u | b | r | 0 | u | t | i | n | е | S | 4   | äh | 4 |    | ta et | 10 | 12 |

| Hard | wa   | r e | 1  | Le  | V  | е  | 1  | F   | ₹e  | g | i | S | t | е | r | S | D |   |     | a  |   | 9  |       | и  | 19 |

| I/   | 0 1  | A d | d! | re  | S  | S  | ir | 18  | ξ a |   | 9 |   | 2 |   | a |   | 8 |   |     | 8  |   |    | *     | 0  | 19 |

|      | 0 1  |     |    |     |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    |       | ۵  | 20 |

|      | ada  |     |    |     |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    |       |    | 20 |

|      | ad,  |     |    |     |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    |       |    | 23 |

|      | ite  |     |    |     |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    |       |    | 23 |

|      | nt   |     |    |     |    |    |    |     |     |   |   |   |   | Z | a | t | į | 0 | n   | 9  |   | 8  |       | 9  | 28 |

|      | ter  |     |    |     |    |    |    |     | a   |   | 9 |   | 8 |   | 8 | 1 | 9 |   | 9   | 8  |   |    |       | ŵ  | 29 |

|      | ftwa |     |    | Dr  | i  | VE | 2  | S   |     |   |   |   |   |   |   |   |   |   |     |    |   |    |       |    |    |

|      | rrar |     |    |     |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    |       |    |    |

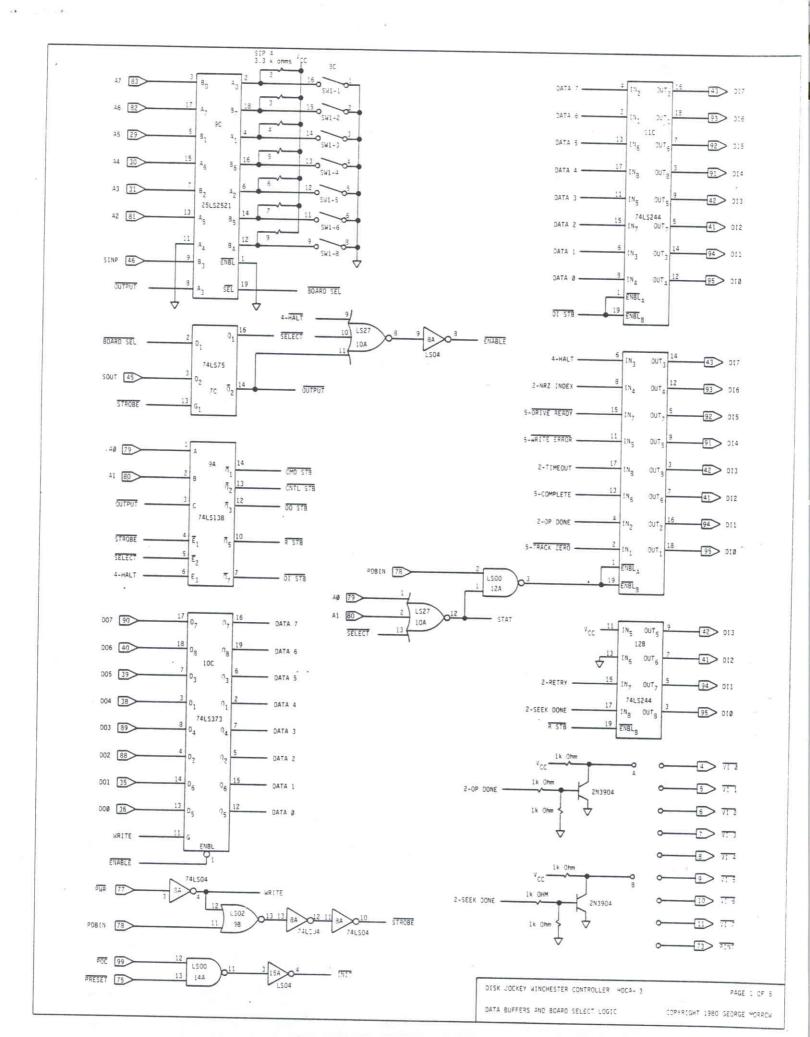

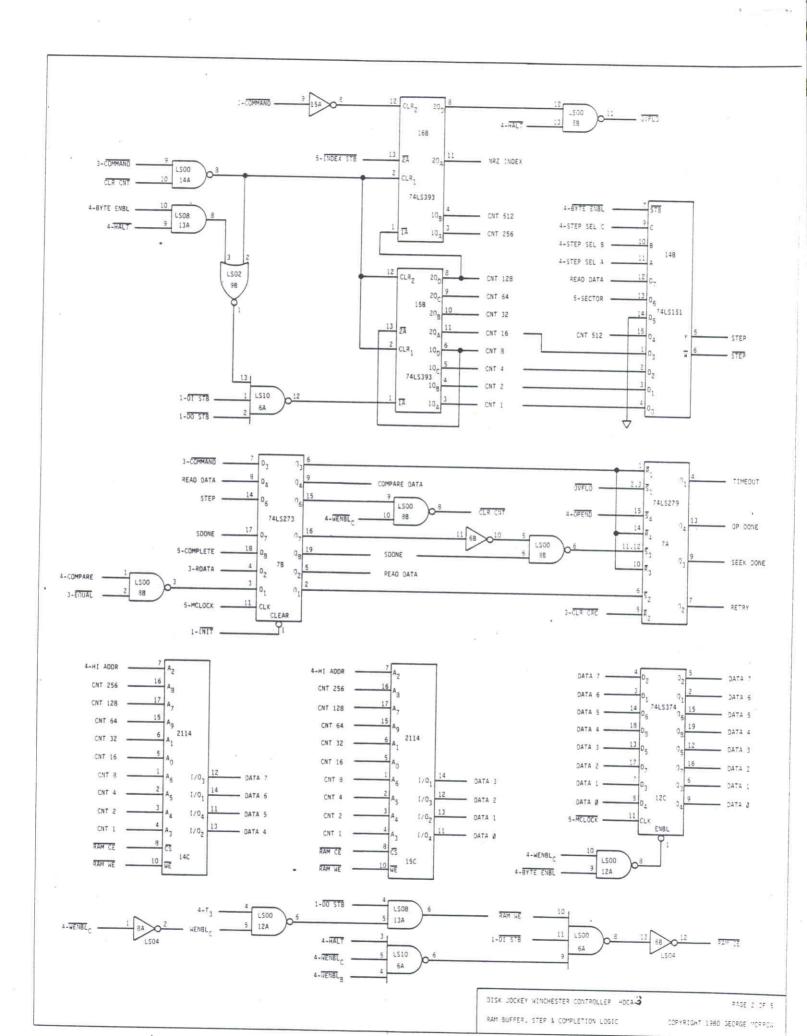

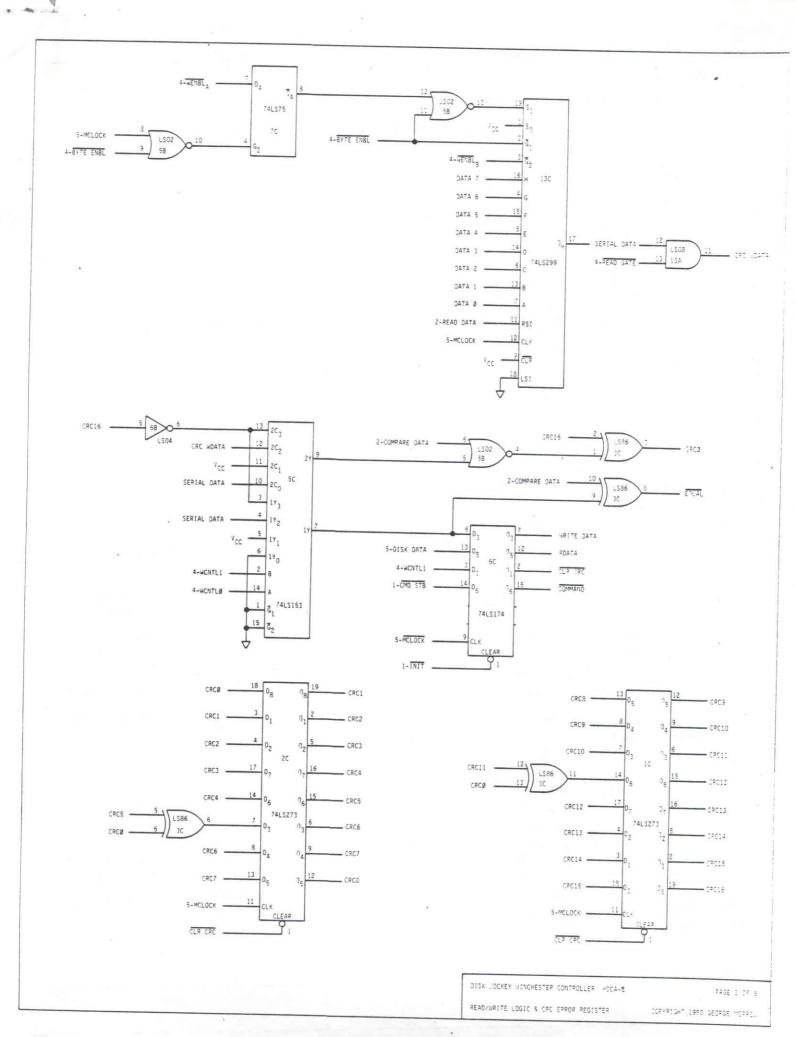

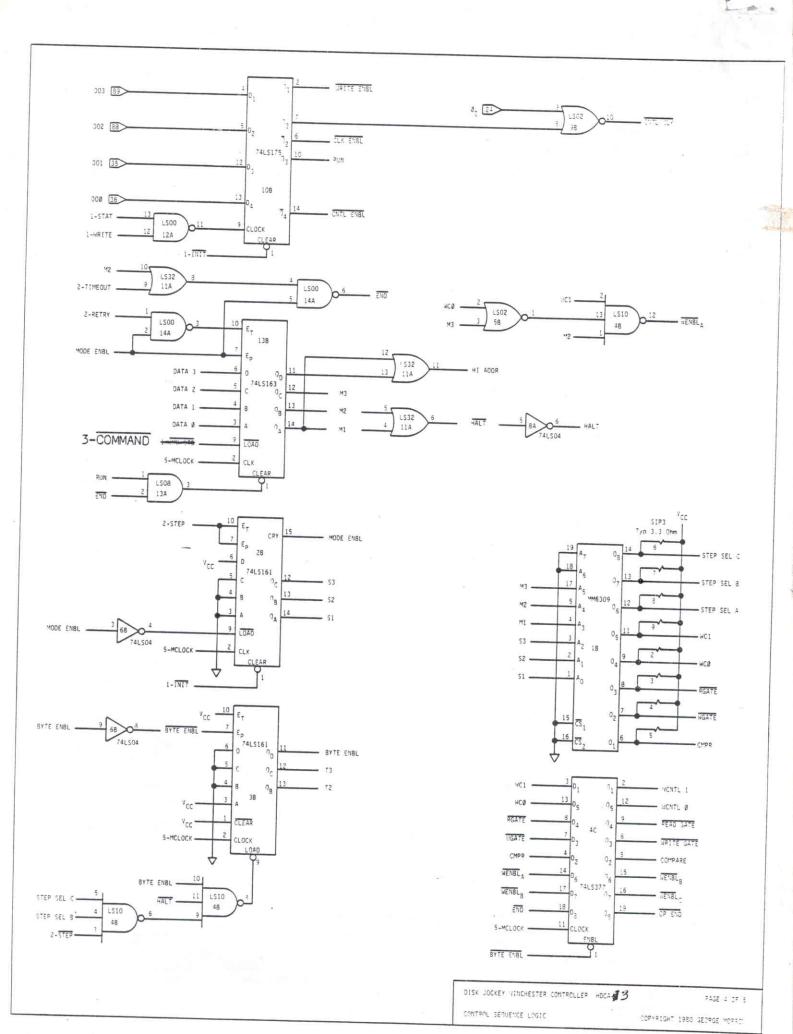

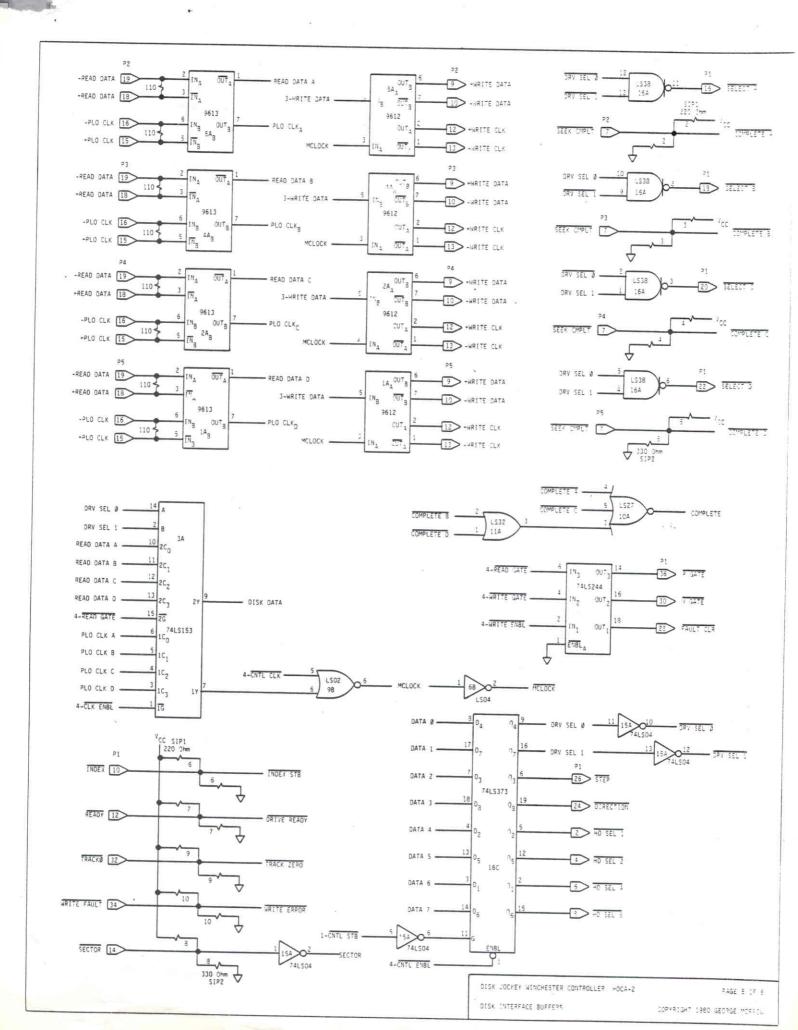

| Sch  | nema | t   | ic | S   |    |    |    |     |     |   |   |   |   |   |   |   |   |   |     |    |   |    |       |    |    |

#### INTRODUCTION

The Discus M26, M20, and M10 are complete mass storage subsystems each consisting of three main components: a winchester type hard disk drive with a formatted storage capacity of 26 million bytes (M26) 20 million (M20) or 10 million bytes (M10) respectively, universal power supply which provides the necessary DC voltages to power the drive, and a controller which establishes a data channel between the disk drive and any S=100 based computer.

The drive and power supply are housed in a cabinet which has been designed for either table top or rack-mount operation. The only extra hardware required to mount the M26 drive in a standard 19" RETMA equipment rack is a pair of rack-mount slides which attach directly to the cabinet. The 8 inch M10 and M20 system is currently supplied in a desk top unit only. The physical dimensions are: 9.06 inches wide, 22.55 inches long and 5.05 inches high.

The controller plugs into any slot of the mother board of an S-100 system and is connected to the drive through a pair of flat cables. One of the cables carries clock and data information and the other carries control and status information. The controller can accommodate up to four drives, so the M26 system can be expanded to a total capacity of 104 million bytes, M20 to over 80 million bytes and the M10 to over 40 million.

The Disk Operating System software supplied with the Discus systems is the popular CP/M version 2.2. It was chosen because of the readily available application software that runs under CP/M. With CP/M, the owner of a Discus hard disk system has access to virtually any software that has been written for an 8080, 8085, or Z80 microcomputer.

A user can communicate with the Discus system on any of three levels: through CP/M, through low level software drivers which are included on the disk, or through direct commands to the Disk Jockey Winchester controller. The protocol for using the system through CP/M are covered in detail by the CP/M manual furnished under separate cover. The details of using the system through the low level software drivers and for using the hardware directly are covered in this manual.

A Winchester type sealed disk drive such as the one with the Discus M26 M20 and M10 has many advantages and also some limitations. Large capacity, low maintenance, and high reliability are the most obvious advantages. The major disadvantage is the fixed nature of the magnetic media. The media of a floppy disk drive can be removed and placed in a secure environment. This is not the case with the present generation of winchester disk drives. The media is sealed inside the unit and cannot be removed. Thus, as long as the drive is connected to a computer, the data written on the magnetic surface of the disk is never really secure.

The present solution to this data security problem is to backup the data periodically on some storage device which has removable media. The most practical device for this job at the present time is a floppy disk system. By using the facilities provided by CP/M, it is quite easy to transfer files from the Discus Hard drive to a floppy disk system such as the Discus 2D or the Discus 2+2. In the near future it will be possible to backup data on a hard disk by using small high density cassette tape drives. Presently the prices of these units are such that a backup system using them costs almost as much as the hard disk system itself. However, manufacturers are designing low cost tape drives that will allow backup tape systems to sell for approximately half the price of a hard disk system = a much better state of affairs. Morrow Designs plans to introduce a cassette tape backup system in 1981.

#### THE SYSTEM BOOTSTRAP

#### INTRODUCTION

The Disk Jockey/Winchester controller contains all the logic necessary to control the drive and to transfer data to and from the disk. It appears to the system as four I/O devices and has no memory in the address space of the CPU. Therefore some other element of the system has the responsibility for the initial load of the operating system and/or utility software from the disk. This initial loading operation is referred to as the bootstrap operation. The purpose of this section is to discuss several ways that the bootstrap operation can be implemented and to

#### IMPLEMENTING THE BOOTSTRAP

The code necessary to perform a bootstrap is roughly 100 bytes long. The least expensive but most troublesome method to bring up the system is to enter this code into memory and execute it. Fortunately there are several alternatives to this process which Morrow's will supply at nominal cost:

- 1. The bootstrap code can be programmed into any of the more common EPROMs: 1702, 5204, 2708, or 2716. Any of these parts are acceptable if supplied by the customer. If the part is to be supplied by Morrow Designs, it will be a 2708. The starting address of the program can be anywhere but must be supplied along with the order.

- The program can be supplied on a CP/M compatible floppy diskette as a command file. In this case the program has a starting address of 100H (Hex) in accordance with the system requirements of CP/M.

- When CP/M 2.2 is supplied with a Discus I or Discus 2D system, the CBIOS software of the CP/M.contains a module which knows that a Discus M26 M20 or M10 system may be attached to the computer and treats it as drives E, F, and G (M26) and (M20) or drives E and F (M10). Drives A, B, C, and D are reserved for floppys.

# THE BOOTSTRAP SOFTWARE

The program listed below will load the disk system software into memory. There is an option which will either load CP/M or only the utility low lever disk drivers. The program starts at location 100H (Hex) but can be easily changed to start at the beginning of any page by altering the third byte of the jump (and conditional jump) instructions to the value of the desired page.

```

1 *HARD DISK BOOTSTRAP SOFTWARE

001:000 303 000 003

JMP START

3

001:003 001:375

```

|                              |                                  |   | 1 *HARD                                | DISK BOOTSTRAP                             | SCFTWARE                                       |

|------------------------------|----------------------------------|---|----------------------------------------|--------------------------------------------|------------------------------------------------|

| 0100                         | 03 00 03                         |   | 2                                      | JMP START                                  |                                                |

| 0103                         | O1FD                             |   | 4                                      | DS 509                                     | room for boot                                  |

| 0300<br>0302<br>0304         | 3E FC D3 52 3E 05                |   | 2<br>3<br>4<br>5<br>6 START<br>7       | MVI A, DRIVE<br>OUT FUNCTN<br>MVI A, DRENB | A select<br>-drive A<br>L turn on drive        |

| 0306 °<br>0308<br>030A       | D3 50<br>DB 50<br>E6 20          |   | 8<br>9<br>10 RLCOP                     | OUT CONTRL<br>IN STATUS                    | -command register test for                     |

| 030C<br>030F                 | C2 08 03                         |   | 11<br>12<br>13                         | ANI READY<br>JNZ RLOOP<br>MVI A, DSKRU     | drive A ready<br>N enable the                  |

| 0311                         | D3 50 DB 50                      |   | 14<br>15 WAITZ<br>16                   | OUT CONTRL<br>IN STATUS                    | -controller test for heads                     |

| 0313<br>0315<br>0316<br>0319 | 1 F<br>D2 2B 03<br>3E F8         |   | 16<br>17<br>18                         | RAR .<br>JNC SDONE<br>MVI A,STEPO          | -at track zero                                 |

| 031B                         | D3 52<br>3E FC                   | - | 19                                     | OUT FUNCTN<br>MVI A, DRIVE                 | -the                                           |

| 031 F<br>0321<br>0323        | D3 52<br>DB 50<br>E6 04          |   | 21<br>22 WAITC<br>23                   | OUT FUNCTN<br>IN STATUS                    | -command wait for                              |

| 0325<br>0328                 | CA 21 03<br>C3 13 03             |   | 24<br>25                               | ANI COMPLT JZ WAITC JMP WAITZ              | -the seek<br>-to complete                      |

| 0323<br>032D<br>032E         | DB 50<br>4F<br>DB 50             |   | 26 SDONE<br>27                         | IN STATUS                                  | get an image<br>-of the status reg             |

| 0330<br>0331                 | 91<br>CA 2E 03                   |   | 28 [WAIT1<br>29<br>30                  | IN STATUS<br>SUB C<br>JZ IWAIT1            | wait for -the index pulse -to arrive           |

| 0334<br>0336                 | DB 50<br>91                      |   | 31 IWAIT2                              | IN STATUS<br>SUB C                         | wait for the -next index pulse                 |

| 0337<br>033A<br>033C         | C2 34 03<br>3E 08<br>D3 51       |   | 32<br>33<br>34<br>35<br>36<br>37<br>38 | JNZ IWAIT2<br>MVI A, HEADER<br>OUT COMMD   | test for head settle reset the -buffer pointer |

| 033E<br>033F                 | ΔF                               | 7 | 36<br>37                               | XRA A<br>OUT DATA                          | -to header area                                |

| 0341<br>0343<br>0345         | D3 53<br>D3 53<br>3E 01<br>D3 53 |   | 38<br>39<br>40                         | OUT DATA MVI A, SECTOR OUT DATA            | track 0<br>l 1 for CP/M<br>-or 30 for drivers  |

| 0347<br>0349                 | 75 80<br>D3 53                   |   | 41<br>42                               | MVI A, SYSTEM                              | system key                                     |

| 034B<br>034D<br>034F         | 3E 01<br>D3 51<br>DB 50          |   | 43<br>44<br>45 WAITD                   | MVI A, DREAD<br>OUT COMMD<br>IN STATUS     | issue a<br>-read command wait for command      |

| 0351<br>0353                 | E6 02<br>CA 4F 03                |   | 46<br>47                               | ANI OPDONE<br>JZ WAITD                     | -to complete                                   |

| 0356<br>0358<br>0359         | DB 53<br>6F<br>5F                | 4 | 48<br>49 -<br>50                       | IN DATA MOV L, A MOV E, A                  | low order byte of -bootstrap address           |

| 035A<br>035C<br>035D         | DB 53<br>67                      |   | 51<br>52                               | IN DATA<br>MOV H, A                        | high order byte of -bootstrap address          |

| 035E<br>0360                 | 57<br>DB 53<br>12                |   | 53<br>54 LLOOP<br>55                   | MOV D,A<br>IN DATA<br>STAX D               | load -the                                      |

| 0361                         | 1C<br>C2 5E 03                   |   | 56<br>57                               | INR E<br>JNZ LTOOP                         | -bootstrap                                     |

| 0365                         | Ξ9                               |   | 58                                     | PCHL .                                     | branch there                                   |

# INTRODUCTION

To do useful work, the operating system must communicate with at least one other I/O device besides the disk. This device is called the SYSTEM CONSOLE and generally consists of a video display and a keyboard. This device allows the user and the operating system to communicate with each other. Depending on overall requirements it may be necessary to attach other I/O devices such as a printer or a modem to the system.

I/O devices vary greatly in their electrical and mechanical characteristics. To communicate with them, allowances must be made for these variances. In order that the operating system be flexible, it must remain aloof to the peculiarities of the devices that it communicates with. Thus, each time a new type of I/O device is connected to the system a communications problem is created. It is resolved by a software module called a "driver". The driver must accept commands from the operating system and translate them into a form that the I/O device will accept. The I/O device is usually connected to the system through an interface which translates the computer's logical signals into the proper electrical signals the device can understand. Generally this interface is a circuit board that plugs into the bus of the computer and is connected to the device through a cable.

In order to create a driver, the user needs to have detailed knowledge concerning (1) how information is passed back and forth between the device and the interface, (2) how the interface and the computer communicate, and (3) how the operating system passes information back and forth to the driver.

Drivers vary a great deal in length and complexity. However, irrespective of their size or intricacy, there is an important observation to be made about the creation of a driver: someone who does not possess a clear and detailed understanding of how BOTH the device and its interface function should never attempt to write the software to drive it. This type of task also presupposes considerable skill in assembly language programming. Faulty or incomplete knowledge of the device or its interface usually results in a program that doesn't work or, worse yet, only partially works. A great deal of time can be wasted and equipment may be damaged in trying to make a bad driver function. If there is any question in the user's mind about how a driver should be written, he should consult with the personnel at the computer store where the system was purchased. In many cases, the driver software will be a stock item and can usually be installed before the system leaves the store.

In many areas there are groups of computer enthusiasts who have joined together in clubs to share knowledge and exchange information. These organizations usually meet at regular intervals and provide an ideal environment to gain experience and sharpen skills in all areas of computing. The user who wishes to learn the art of creating device drivers will benefit from joining one of these groups because of the wide range of skills its members possess.

This section of the manual discusses how information is passed back and forth between the operating system and the driver. Also presented are several sample drivers for the system console which interface to some of the more common S=100 computers.

#### THE I/O DRIVER JUMP TABLE

CP/M maintains a table of jump instructions in high memory. Each entry in this table points to an I/O driver that the operating system may have occasion to use. There are 17 entries in this table. Only 6 of these are of concern to the user since the others point to disk drivers. The table, as it appears in memory, is presented below. The entries marked with an asterisk are the ones of interest to the user and will be discussed in detail.

JMP BOOT ; arrive here from a cold start load JMP WBOOT ; arrive here for warm start \*JMP CONST \*JMP CONIN \*JMP CONOUT ; check for console character ready ; read console character in :write console character out \*JMP LIST \*JMP PUNCH ;write listing character out \*JMP PUNCH ; write character to punch device \*JMP READER ; read the reader device JMP HOME . ; move to track 0 on selected disk JMP SELDSK :select disk drive JMP SETTRK ; set track number JMP SETSEC ; set sector number JMP SETDMA ; set data transfer address JMP READ ; read selected sector JMP WRITE ;write selected sector JMP LISTST return list status JMP SECTRAN ; sector translate subroutine

At location 0 in memory CP/M maintains a jump instruction to the second entry of this table - JMP TABLE+3 (to WARM BOOT). The value in location 2 is the page number that table starts on. In almost all operating systems, the jump table starts at the beginning of a page which means the value of location 1 will be 3.

The DISCUS M26 M20 and M10 disk systems are shipped with two types of I/O configurations:

# System I/O requirements

- 1. Preinstalled drivers which interface to

- a. DISCUS 2D floppy disk controller

- b. SWITCHBOARD I/O controller board

- c. SOL computer

- d. EXIDY computer

- 2.No installed drivers each entry in the table marked with an asterisk is a "jump to self" instruction

#### INSTALLING I/O DRIVERS

In systems which have no installed drivers, there is a 512 byte section of memory immediately following the jump table reserved for drivers user needs to furnish. In some instances it may not be necessary to install all six of the drivers listed above. For instance, if there is no punch device in the system, the punch device driver would consist of a single RET(urn) instruction. The following procedure should be used to install the necessary drivers:

- 1. Study carefully the CP/M 2.2 Alteration Guide section of the CP/M documentation manual.

- 2. Code and assemble the drivers one by one.

- 3. Enter the assembled code into the reserved 512 byte memory area immediately following the jump table.

- 4. Alter the "jump to self" instructions so as to point to the newly installed drivers.

- 5. Test and debug the drivers.

- 6. When a driver functions correctly execute the SAVEUSER command. This command automatically alters the operating system so the driver is loaded back into memory when the system boots.

- 7. Save a copy of the source code for the drivers on a file on the disk. If the operating system is made larger (or smaller) the drivers can be reinstalled with a minimum of effort.

#### I/O DRIVER SPECIFICATIONS

All simple character I/O operations are assumed to be performed in ASCII, upper and lower case, with high order (parity bit) set to zero. An end-of-file condition for an input device is given by an ASCII control-z (1A hex). Peripheral devices are seen by CP/M as "logical" devices, and are assigned to physical devices within the CBIOS (see the CP/M documentation).

In order to operate, the system needs only the CONST, CONIN, and CONOUT drivers (LIST, PUNCH, and READER may be used by application programs, but not by the CCP). The LISTST entry is currently used only by DESPOOL, and may be a simple RET instruction.

#### DEVICES

CONSOLE The principal interactive console which communicates with the operator, accessed through CONST, CONIN, and CONOUT. Typically, the CONSOLE is a device such as a CRT or Teletype.

LIST The principal listing device, if connected to the system, is usually a hard copy device such as a printer or Teletype.

PUNCH The principal tape reading device, such as an optical reader or Teletype.

Note that a single peripheral can be assigned as the LIST, PUNCH, and READER device simultaneously. If no peripheral device is assigned as the LIST, PUNCH, or READER device, the driver that the user creates may give an appropriate error message so that the system does not "hang" if the device is accessed by PIP or some other user program. Alternately, the PUNCH and LIST drivers can just simply return, and the READER driver can return with a 1A (hex) in register A to indicate an immediate end-of-file.

#### DRIVERS

CONST Sample the status of the currently assigned console device and return OFFH in register A if a character is ready to read, and OOH in register A if no console characters are ready.

CONIN Read the next console character into register A, and set the parity bit (high order bit) to zero. If no console character is ready, wait until a character is typed before returning.

CONOUT

Send the character from register C in the console output device. The character is in ASCII, with high order parity bit set to zero. You may want to include a time out on a line feed or carriage return if your console device requires some time interval at the end of the line (such as a TI Silent 700 terminal). You can, if you wish, filter out control characters which cause your console device to react in a strange way (a control-z causes the Lear Seigler terminal to clear the screen, for example).

LIST Send the character from register C to the currently assigned listing device. The character is in ASCII with zero parity.

# System I/O requirements - Driver Specifications

- PUNCH Send the character from register C to the currently assigned punch device. The character is in ASCII with zero parity.

- READER Read the next character from the currently assigned reader device into register A with zero parity (high order bit must be zero), and end-of-file condition is reported by returning an ASCII control-z (1AH).

#### INTRODUCTION

There are applications which require a more intimate degree of control over the disk than is possible through the operating system. On the other hand, it may not be desirable or necessary to communicate directly with the controller through hardware registers. A set of low level software drivers is included with the system to meet the foregoing needs. These drivers can be loaded directly from the system tracks through an option in the bootstrap loader. The source code has also been provided in a file called HDFIRM.ASM. This file can be accessed through the operating system if the user needs to modify it. The code has been assembled to run starting at 370:000 Octal (OF800 Hex). A change in the "origin" statement of the file will allow the code to be assembled for other starting address.

#### THE DISPATCH JUMP TABLE

To use the low level drivers, the user should branch to the appropriate address in a jump table in the first few words of the driver software. Since each subroutine ends with a RET(urn) instruction a CALL instruction should be used to branch to it.

The jump table contains jump instructions that point to the true address of a utility routine within the software. Having a jump table allows the individual routines to be updated and moved without having to change software that calls the routines. Let A represent the address of word 0 of the driver software. In the standard version, A = 370:000Q (F800H). The addresses to call for the utility routines are then:

| ADDRESS | STANDARD | VALUE | SYMBOLIC<br>Value | FUNCTION                      |

|---------|----------|-------|-------------------|-------------------------------|

| Æ       | Octal    | Hex   |                   |                               |

| A       | 370:000  | F800  | TRKZRO            | Recalibrate (seek to track 0) |

| A+3     | 370:003  | F803  | TRKSET            | Seek to a track               |

| A+6     | 370:006  | F806  | SETSEC            | Select a sector               |

| A+9     | 370:011  | F809  | SETDMA            | Set the data transfer address |

| A+12    | 370:014  | F80C  | DREAD             | Read a sector of disk data    |

| A+15    | 370:017  | F80F  | DWRITE            | Write a sector of disk data   |

| A + 18  | 370:022  | F812  | SELDRV            | Select a disk drive           |

| A+21    | 370:025  | F815  | DMAST             | Read data transfer address    |

| A+24    | 370:030  | F818  | STATUS            | Disk status input             |

| A+27    | 370:033  | F81B  | STHEAD            | Select a read/write head      |

| A+30    | 370:036  | F81E  | SETKEY            | Set the "key" for a sector    |

The specific function of each subroutine is described below.

A subroutine completes by executing a RET instruction. If the routine completes normally, it returns with the carry flag cleared. If an error is detected, the carry flag is set. A map of the error conditions is placed in the CPU's A register. A program should always test the carry flag after a return from a disk utility subroutine and branch to an appropriate error handling routine if the carry flag is set.

#### DISK I/O

To understand the significance of the disk utility software, it is necessary to say a few words about how data is organized on the disk.

Information on the disk is organized into concentric tracks. The number of tracks varies depending on the DIscus System you have ordered. The M26 has 202 tracks while both the M20 and M10 contain 244 per platter. The disk read/write heads can be moved to any track by a series of step in or step out commands. A step in command moves the read/write heads one track towards the center of the disk. A step out command moves the heads one track away from the center of the disk. The numbering of the tracks is arranged so that track zero is farthest from the center.

There are two rotating platters inside the drive and both the upper and lower sides of the platter are used to store magnetic information. Floating over each surface is a pair of read/write heads mounted side by side and spaced so that when the outer head is positioned over its inner most track, it is still farther away from the center of the platter than the inner head is when positioned over its outer most track. That is, track zero for the inside head is closer to the center of the platter than track 201 (M26) or 243 (M10\M20) is for the outside head. There are a total of eight heads on the M26 two for each surface. The M20 system contains a total of 8 heads per drive one for each surface. The M10 system contains a total of four heads one for each surface.

Once the read/write heads have been moved to the desired track, the rotation of the disk will move a circle of magnetic material beneath (or above) each of the heads. Within these eight circles data is recorded in distinct regions called sectors. The sector is the smallest amount of information that can be separately read from or written to the disk and each one contains 512 bytes of data.

In the header field which precedes the data field of a sector, the track number, the head number, the sector number, and data security information are recorded. During read or write commands, this header is read before data transfers take place.

The disk drive has a sensor that reports when the read/write heads are physically positioned at track zero. A series of step out commands must be issued by the controller until this status line becomes active. This operation will always position the head to the same physical track. The seek to track zero command is often called a recalibrate command and is a standard utility subroutine supplied with the disk software. Whenever the heads are moved to another track, the disk drivers must account for this change in position so that when read or write commands are issued, correct track information is passed to the controller.

Transferring a sector of disk data between memory and the disk involves the following steps (each corresponding to a subroutine call to the disk utility software, with the exception of error checking):

- 1. Specify the track number the read/write heads should be positioned over during subsequent data transfers between the disk and memory. There are a total of 202 tracks, numbered 0 through 201 on the M26. There are a total of 244 tracks, numbered 0 through 243 on the M10\M20.

- 2. Check for error conditions.

- 3. Specify a head to be selected during subsequent read or write operations. There are a total of eight and are numbered 0 through 7 on the M26/M10 The M10 has a total of 4 heads which are numbered 0 to 3.

- 4. Specify a sector number that will be involved in subsequent data transfers between the disk and memory. There are a total of 32 sectors numbered 1 through 32 for the M26. There are a total of 21 sectors numbered 1 through 21 for the M10\M20.

- 5. Check for error conditions.

- 6. Specify the starting memory address of the block of data to be transferred to or from the disk.

- 7. Perform the read or write operation.

- 8. Check for errors.

#### DISK UTILITY SUBROUTINES

TRKZRO - This subroutine positions the read/write heads to the outermost track of the disk platters: track 00. The track zero sensor is used to determine this positioning. Except for track 00, the drive has no way to know where the read/ write heads are positioned. It is one of the responsibilities of the disk utility software to always know over what track the heads are positioned. In general, when a drive is first selected, the track position of the heads is not known. Thus, the TRKZRO routine should be called. In fact, if there is ever any doubt about the position of the heads this routine should be called.

TRKSET - This routine will issue the proper commands to the drive to position the read/write heads over the track which is specified by the CPU's C register. The value in the C register should be between 0 and 201 (decimal) for the M26 and 0 to 243 for the M10\M20  $\bullet \bullet$  A value outside of these bounds will cause the routine to abort with the carry flag set and bit 6 of the A register set. A test is performed to make sure the controller is not busy processing data transfer command. Also, the status of the most recently selected drive is tested. If the controller is busy, or the drive is not ready, the carry bit is set and the routine aborts. As before, the A register will indicate the type of error that was encountered: if bit 1 is set, the controller was busy. If bit 5 is set, the drive was not ready. If there are no error conditions, the routine issues a series of step pulses to the drive so to move the read/write heads to the proper track. This series of step commands is issued much faster than the heads can move. This does not pose a problem however, since the drive has the ability to buffer and collect pulses that arrive too rapidly. This ability enhances the performance of a multiple drive system: after a series of step commands are issued, it is possible to deselect the drive and select another. In this way, one drive can be moving its heads to a new track while another is transferring data. This type of operation is called overlapped seek. The logic of the TRKSET routine has been designed to allow as many overlapped seeks to occur as is practical. Care has been taken so that waits encountered for head settle times are shared whenever possible.

SETSEC - This routine allows the user to specify what sector will be involved in the next data transfer operation between the disk and memory. The sector number is passed by the C register of the CPU. It should be between 1 and 32 (decimal) for the M26 and 1 and 21 (decimal) for the M10\M20. If the value in C is outside these bounds, the carry flag is set and the routine aborts.

- SETDMA During disk transfer operations, blocks of data move to and from the disk. These blocks are 512 bytes long. The starting address (in memory) of a data block that will be involved in the next disk transfer operation is specified by the contents of the B-C register pair when the SETDMA routine is called. The high order byte of the address is in the B register and the low order byte is in the C register. This routine cannot produce an error.

- DREAD This subroutine transfers information from the disk to memory. If the controller is busy or if the drive is not ready, the routine aborts with the carry flag set. Error information is detailed below. The drive involved in the operation is one specified by the most recent call to the SELDVR routine (see below). The position of the read/write heads is determined by the latest call to the TRKSET routine which involved the presently selected drive. The head number and sector number is given by the most recent calls to the STHEAD routine (see below) and SETSEC routine respectively. The starting memory address where the transfer will occur is specified by the most recent call to the SETDMA routine. If the drive is ready and the controller is not busy, DREAD issues a series of commands to the controller which will cause it to transfer information from the proper sector of the disk to its internal buffer. If any errors have occured, the carry flag is set and the routine aborts without transferring data from the controller to memory. If the transfer is free of errors, the data is moved from the controller's buffer into memory starting at the address specified by the last call to SETDMA.

#### "DREAD" REGISTER A ERROR BITS

|        |     | 7   | 6   | 5 | 4 | 3   | 2 | 1  | 0 |     |       |

|--------|-----|-----|-----|---|---|-----|---|----|---|-----|-------|

|        |     |     |     | 1 |   | - 1 |   | 1  | 1 |     |       |

|        | NOT |     |     | ! |   | 1   |   | 1  | 1 | CRC | ERROR |

| RECORD | NOT | FOU | ND_ |   |   |     |   | 1_ |   | BUS | Č.    |

The "RECORD NOT FOUND" bit indicates that the external software has not selected the proper key to access the sector in question. If the "RECORD NOT FOUND" bit is set, the "CRC ERROR" bit should also be set. On rare occasions, error bits 0 and 3 will indicate that the header of the sector contains bad data or that a flaw exists in the magnetic media at this area of the sector. The bad data can be corrected or the media flaw can be detected through the use of diagnostic software covered in the next section of this manual. If CRC ERROR is 1 and the others bits are 0, an error was made in reading the data in the "data" area of the sector. When data is written to the disk, a binary polynominal is created from the serial stream as it is transferred to the disk. This polynominal is divided by a fixed prime polynominal of order 16 until a remainder of less than 16 is produced. The data bits of this remainder are appended to the end of the data

When a sector is read back from the disk, the same polynominal is recreated by the serial stream except that the remainder polynominal at the end is appended to the stream. Thus when the original prime polynominal is now divided into the new one, there will be a zero remainder if there have been no read errors. If there were read errors, the division will produce a remainder. If this remainder is non zero, the CRC error bit in the A register is set. The hardware in the controller which implements the CRC logic may not, at first glance, appear to function as described above. The hardware takes advantage of the fact that the division can be done while the polynominal is being created. Normally, when the hardware detects a CRC error, the calling software will try to re read the data. After 10 trys if the data is still bad, a hard error is reported. In this case, diagnostic software should be used to test the integrity of the magnetic media in this sector and place it in the bad sector file if necessary.

DWRITE - This subroutine transfers information from memory to the disk. If the controller is busy or if the drive is not ready, the routine aborts with the carry flag set. A map of the error bits is presented below. The drive involved in the operation is the one specified by the most recent call to the SELDRV routine (see below). The position of the read/write heads is determined by the latest call to the TRKSET routine which involved the presently selected drive. The head and sector number are given by the most recent calls to STHEAD (see below) and SETSEC routines respectively. The starting memory address where the transfer will occur is specified by the most recent call to the SETDMA routine. If the drive is ready and the controller is not busy, a block of data 512 bytes long is transferred to the controller's buffer from memory. DWRITE then issues a series of commands to the controller which cause the controller to write the data in its buffer to the proper sector on the disk. If any errors occur, the carry flag is set and the A register is loaded with the proper error bits.

#### "DWRITE" REGISTER A ERROR BITS 6 2 1 1 NOT READY 1 CRC ERROR RECORD NOT FOUND BUSY WRITE FAULT

For disk write operations, the "CRC ERROR" and "RECORD NOT FOUND" bits should always be set together. This type of error condition is discussed above in the DREAD routine. The "WRITE FAULT" bit is an indication of an exceptional condition at the drive during the time the WRITE GATE signal is active. For details, see the drive manual included in the documentation. This bit should never be set if the hardware is functioning correctly and there are no faults in the cables which connecting the controller to the drive(s).

- SELDRV The value of the C register determines which one of four drives is to be selected. Only the two low order bits of register C are used for drive selection. The routine tests the "drive ready" status and delays approximately 2 minutes if the drive has not been selected before. The reason for this long wait is that it may take this long for the drive to stabilize when power is initially applied. If the drive is not ready, the routine returns with the carry flag set.

- STATUS The controller has two status registers. One is a full 8 bits wide while the other is only 2 bits wide. This routine reads the first status byte into the A register and the two bits of the second status register into the B register. The meaning of the various bits are detailed next.

# THE A STATUS REGISTER

|       |        | 7 | 6 | 5 | 24 | 3 | 2  | 1  | 0 |          |

|-------|--------|---|---|---|----|---|----|----|---|----------|

|       |        | 1 | 1 | 1 | 1  | 1 | 1  | 1  | 1 |          |

|       | HALT   | 1 | 1 | 1 | 1  | 1 | 1  | 1  | 1 | TRACK O  |

|       | INDEX_ |   | 1 | 1 | 1  | 1 | 1  | 1_ |   | OP DONE  |

|       | READY_ |   |   | ! | 1  | 1 | 1_ |    |   | COMPLETE |

| WRITE | FAULT_ |   |   |   | 1  | ! |    |    |   | TIME OUT |

#### THE B STATUS REGISTER

7 6 5 4 3 2 1 0 | | SEEK DONE

- HALT When this bit is a 1, the controller is halted and not presently executing a command. When this bit is a zero, the controller is either preparing to execute a command or in the process of executing a command.

- INDEX The level of this bit changes whenever an index pulse is transmitted from the presently selected drive.

- READY When this bit is a 1, the presently selected drive is "ready" and can respond to commands from the controller. When this bit is a 0, the drive is not ready and will not respond to controller commands.

WRITE FAULT - When this bit is a 1, it indicates there was an exceptional condition present the last time the WRITE GATE signal to the drive was active. An example of an exceptional condition is that both READ GATE and WRITE GATE were active at the same time. It is possible that WRITE FAULT will be active when power is first applied to the drive. However, DRVSEL will always reset WRITE FAULT when the drive is initially selected. This bit indicates there is a hardware fault of some kind; either in the drive, the controller, or the connecting cables. Normally, this bit will be a 0.

TIME OUT - This bit is set to a 1 whenever the command the controller is executing takes longer than 8 revolutions of the disk. When the controller starts to execute a command, a counter is enabled which is clocked by index pulses from the drive. If the command is still in progress after 8 revolutions, the TIME OUT bit is set and the command in progress is terminated. If this bit is set after a transfer operation, it is an indication that the "key" field in the sector header on the disk does not match the key that the disk drivers have been given. When this bit is set, the RETRY bit in the B register should also be set. Normally, the "key" field of the sector header has a zero value. For the disk utility software discussed in this section of the manual the default value for the key is zero. Unless a call was made to the SET KEY special routine to change the key, the TIME OUT bit should always be zero. The one exception to this rule is if there is a hard data error in the header field of the sector. Usually this will mean there is a flaw in the magnetic media and this sector should added to the BAD SECTOR file.

COMPLETE - When this bit is a 0, there is a drive in the system which has received one or more step commands and is in the process of moving its heads from one track to another. A drive does not have to be selected to affect this bit. When this bit is a 1, all the drives in the system have completed their seeks.

OP DONE - When this bit is a 1, it indicates that the controller has completed some kind of transfer command. Unlike HALT, this bit will be reset whenever a command is issued to the controller - even a NOP command. Once reset, it will remain 0 until another transfer operation is completed.

# Programming Specifications - Utility Subroutines

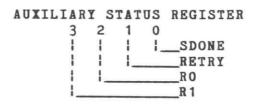

- RETRY When the retry bit is set, a CRC error of some kind was made during the most recent transfer operation between the disk and the controller. If the CRC error was in the header area of the sector, the TIME OUT bit will also be set. If the error was in the data area of the sector, the TIME OUT bit will be zero. Once set, this bit will remain set until a transfer operation occurs in which there is not a CRC error.

- SEEK DONE This bit is set whenever the COMPLETE bit makes a transition from zero to one. As with OP DONE, it is reset by any command to the controller.

- This routine selects one of eight read/write heads on the M26\M20 or one of four read/write heads on the M10. The least significant three bits of the C register determine which head will be selected. The heads are numbered 0 to 7 on the M26\M20 and numbered 0 to 3 on the M10 disk systems. Once a head is selected it will remain selected, even if a different drive is selected. No errors are reported by this routine.

- SETKEY This routine is used to pass a new sector access key to the disk utility software. There are six bytes in the header field of a sector. These are detailed below:

| 1  |      | 1     |       | 1   |        | 1   |     | 1   |       | -   |       | -,  |

|----|------|-------|-------|-----|--------|-----|-----|-----|-------|-----|-------|-----|

| 1  | HEAD | 1     | TRACK | 1   | SECTOR | 1   | KEY | 1   | CRCHI | 1   | CRCLO | 1 2 |

| 1_ |      | _   _ |       | _!_ |        | _!_ |     | _!_ |       | _ _ |       | _1  |

When the controller is issued a read or write command, it scans sector headers until it finds the correct one. However, it demands more than just the correct sector number. The number of the selected head must agree with the value of the first byte of the header field. The track number that the heads are positioned over must agree with the value of the second byte of the header field. The value of the fourth byte of the header field must be a zero or must agree with the what was passed in the C register during the most recent call to the SETKEY routine. Finally, the value of the two CRC error detection bytes must produce a zero remainder for the controller hardware. If all these requirements are satisfied, the controller will proceed to transfer a sector of data to or from the disk. Thus, the "key" field of the sector header allows for 256 levels of security for each sector of data. Except on track 0, this "key" field is normally a zero. By using the software described in the next section, this field can be altered and even read. The purpose of the SETKEY routine is to allow a user access to sectors which have a key different from zero.

#### INTRODUCTION

Users desiring a greater degree of control over the disk than afforded by the software drivers described previously may wish to refer directly to the I/O device registers on the Disk Jockey Hard Disk Controller. There are seven one byte registers. Three are read only, three are write only and one is read/write. These registers occupy four locations in the I/O address space of the system. They may appear anywhere in this space. The only restriction being that the lowest of the four addresses must be divisible by four.

#### I/O ADDRESSING

At location 8C on the circuit board, there is an eight position DIP switch used to determine the starting address of the controller. One of the switches is not used and another serves as a board enable. The other six are connected to a comparator which compares switch settings with I/O addresses on the bus. If there is a match and the board is enabled, I/O commands are allowed to access the controller. Below is a layout of this DIP switch.

| OFF |    | ON |           |        |

|-----|----|----|-----------|--------|

| 1   | 1  | 1  | <br>ADDR  | 7      |

| 1   | 2  | 1  | <br>ADDR  | 6      |

| 1   | 3  | 1  | <br>ADDR  | 5      |

| 8   | 14 | 1  | <br>ADDR  | 4      |

| 1   | 5  | 1  | <br>ADDR  | 3      |

|     | 6  | 1  | <br>ADDR  | 2      |

| 8   | 7  | 1  |           |        |

| 1   | 8  | 1  | <br>BOARI | ENABLE |

|     |    |    |           |        |

As an example of addressing the Disk Jockey HD Controller, the following switch settings will address the board to respond to I/O addresses 120Q through 123Q (50H = 53H):

| SWITCH | SETTING |

|--------|---------|

| 1      | ON      |

| 2      | OFF     |

| 3      | ON      |

| ц      | OFF     |

| 5-8    | ON      |

# I/O REGISTER MAP

Let A represent the address of register 0 of the controller. In boards with standard addresses, A = 120Q (50H). The addresses of the controller registers are then:

| Address    | Standard<br>Octal | Value<br>Hex | Symbolic Value             | Function                                          |

|------------|-------------------|--------------|----------------------------|---------------------------------------------------|

| A<br>A + 1 | 120<br>121        | 50<br>51     | STATUS/CONTL<br>COMD\RESUL | Status/Control Port<br>Command\Aux Status<br>Port |

| A+2<br>A+3 | 122<br>123        | 52<br>53     | FUNCTN<br>Data             | Drive Function Port<br>Controller Data port       |

#### READABLE REGISTERS

Register 0 - The Main Status Port for the Controller and Drive.

Location 120Q (50H) in the standard system.

This register contains bits that identify the current status of the Disk Jockey Controller and the currently selected drive. The details of this register are presented below:

# CONTROLLER STATUS REGISTER

|         | 7  | 6 | 5  | 4 | 3  | 2  | 1  | 0  |        |

|---------|----|---|----|---|----|----|----|----|--------|

| HALT_   | _1 | 1 |    | 1 | 1  | 1  | 1  | 1_ | TRACKO |

| ILEVEL_ |    | _ | 1  | 1 | 1  | 1  | 1_ |    | OPDONE |

| NREADY_ |    |   | _! | 1 | 1  | 1_ |    |    | COMPLT |

| NFAULT_ |    |   |    | _ | 1_ |    |    |    | TIMOUT |

HALT - This is the "not busy" flag of the controller. When the Disk Jockey is not executing a command, this bit is a 1. When a data transfer command is strobed into the command register, the halt bit is reset to 0. At this point the controller is busy and will not respond to new commands until the HALT bit is again 1. Moreover, while HALT is 0 the CPU does not have access to the internal data bus and therefore cannot read from or write to the controller's data buffer. A program interfacing directly to the Disk Jockey controller should monitor this bit to determine when a command completes. The Main Status Register interfaces directly to the S-100 DI (Data Input) bus to allow the system to have access to the status port regardless of the state of the controller.

ILEVEL - This bit changes state with each index pulse from the currently selected drive. Drives that are not selected or not ready cannot transmit index pulses. Thus, ILEVEL only toggles when the selected drive is ready.

NREADY - This bit is a 0 only when the currently selected drive is powered up and ready to receive commands or transfer data.

- NFAULT Each drive in the system, when selected, sends a negative logic signal to the controller called WRITE FAULT. NFAULT monitors this line. WRITE FAULT is active (at a 0 level) if an illegal logic condition existed during a data transfer to the drive. An example of an illegal logic condition is READ GATE and WRITE GATE were active at the same time. This could happen, for example, if the 50 conductor cable between the controller and the drive were installed upside down at one end. There are also other conditions which could occur internal to the drive which can cause WRITE FAULT to be active (see the drive manual for details). Occasionally, WRITE FAULT is active when a drive is first powered up. The utility software, as a matter of course, resets WRITE FAULT on drives that it selects for the first time. Under normal conditions, NFAULT is 1.

- TIMOUT This bit is the latched output of a counter which is clocked by index pulses from the currently selected drive. The counter is enabled when the controller is busy. If a command is in progress after 16 revolutions of the disk, TIMOUT is set to 1 and the command is terminated. This insures that the controller will never "hang" trying to complete a command. Typically, this bit is set when the controller is asked to search for a sector header image that does not exist on the current track. TIMOUT is reset whenever a new command is sent to the controller.

- COMPLT Each drive in the system (which is ready) sends a negative logic signal to the controller called SEEK COMPLETE. This signal is present even if the drive is not selected. When a drive receives a head step command (or a burst of head step commands), logic inside the drive sets the SEEK COMPLETE line false. While the heads are moving to a new track this signal remains false. SEEK COMPLETE goes active again just as the heads have stopped (but not settled). When all the SEEK COMPLETE lines from the drives are active, COMPLT is 1. If any drive's heads are in motion, COMPLT is 0.

- OPDONE This bit is set to a 1 whenever the controller finishes a data transfer command. It is reset whenever any command is issued to the controller.

- NTRCKO This bit is 0 when the heads of the currently selected drive are positioned over track zero. If the heads are over any other track, NTRKO is 1.

Register 1 - Auxiliary Status Port for the Controller and Drive.

Location 121Q (51H) in the standard system.

This register is four bits wide and contains the auxiliary status information regarding the drive and controller. The details of these bits are presented below:

RO,R1 - These two bits are used by the controller to inform external software as to the revision level of the board. The encoding scheme for RO and R1 is given below:

| 1 | R 1 | RO  | rev level |

|---|-----|-----|-----------|

| - |     |     |           |

| ! | 1   | 1 1 | 0         |

| 1 | 1   | 0   | 1         |

| 1 | 0   | 1 1 | 2         |

| 1 | 0   | 0   | 3         |

| 1 |     | 1   |           |

RETRY - This bit is set to 0 whenever a command is issued to the controller. During transfers from the disk, the serial data stream is routed to two places: the shift register where the data is assembled into 8 bit bytes for storage in the data buffer and to the CRC logic where polynominal division is performed. The last 16 bits of any transfer is the CRC error check word. These bits are not stored in the buffer. The last task of any command that transfers data from the disk to the controller is to compare the contents of the CRC register with the CRC error check word. If an error occurs, RETRY is set to 1. Thus, RETRY is the "read data" error flag. If RETRY is high after a read command AND the TIMOUT bit of the main status register is 0, the calling program should read the data again. If RETRY remains high through 10 trys, a hard error is present on the sector. When the controller is asked to search for a sector header image that does not exist on the current track, both TIMOUT and RETRY will be high. If both TIMOUT and RETRY are high then (1) the track is not formatted, (2) there is a hard error in a sector header field, or (3) the controller has an improper sector header image their header area of its data buffer (this is the most likely of the three possibilities).

SDONE - Whenever the COMPLT bit of the main status register makes a transition from 0 to 1, SDONE is set to 1. Any command to the controller will clear SDONE to 0.

#### READ/WRITE REGISTERS

Register 2 - The Controller Data Port.

Location 123Q (53H) in the standard system.

When the controller writes data to the disk, it is taken from an on board 1024 byte buffer. Conversely, when data is read from the disk, it is stored in this same buffer. Register 2 is the window between this buffer and the CPU. This register is used to fill the buffer before write commands are issued and to empty it after reads commands have completed.

Associated with the data port is a pointer which serves to address different locations of the on board data buffer. It is incremented after references to the data port. The pointer can be reset to either half of the buffer by commands to the controller (refer to the command port). Each half of the buffer is 512 bytes long. One half is for data, the other is for sector header information. The controller uses only the first six bytes of the header half of the buffer - the remainder is available to the system.

Data is transferred to the buffer by first resetting the pointer and then initiating successive references to this register. The address pointer will automatically increment after each reference. After data is written in the buffer, it will remain stable unless a disk write command is issued or new data is written to the buffer by the CPU. Likewise, once a disk read operation has loaded the buffer, the CPU may retrieve data from it as often as desired.

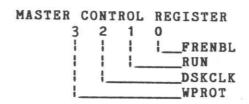

### WRITE ONLY REGISTERS

Register 3 - The Control Port.

Location 120Q (50H) in the standard system.

This is a four bit wide register which functions as the master control port for the board. The four high order data bits are ignored. The function of each low order bit is outlined below:

- WPROT This bit serves two purposes, depending on the state of the NFAULT bit of the main status register. When WPROT is 1, the currently selected drive will be write protected as long as there are no write fault conditions present. If NFAULT=0, WPROT will reset a write fault condition when it is brought high and then low. The drive is write enabled when WPROT is 0 and NFAULT is 1. That is - the disk will accept write commands if there are no write faults present and the write protect bit, WPROT, is low.

- DSKCLK This bit determines how the master clock of the controller will be driven. If DSKCLK is 0, the master clock signal on the board will come from PHASE2 Pin 24 on the S-100 bus. If DSKCLK is 1, the currently selected drive will furnish the master clock to the controller. During data transfers, DSKCLK must be 1. However, if the selected drive is not ready or has encountered a write fault condition, it does not transmit any clock signals. In such a situation, the DSKCLK bit should be brought low so the controller will respond to commands.

- RUN When this bit is 0, the controller is reset and halted.

It will not respond to commands not even the buffer pointer reset commands. This bit is the master enable signal for the controller and should be set to 1 just after the first drive in the system is ready and does not have a write fault condition pending.

- FRENBL This bit enables the output of the drive select and drive function register. The function register outputs are TRI-STATE drivers that can be enabled or disabled. When FRENBL is 0, these drivers are disabled. When this bit is 1, the drivers are enabled.

Each bit in the control port is cleared to a zero whenever the S-100 bus signals POC (pin 99) or PRESET (pin 75) are active. Thus, the drive function register's outputs are disabled, the controller is in a reset state (with RUN false), the master clock is driven by PHASE2, and the disk is write enabled.

Register 4 - The Drive Select and Drive Function Porta Location 122Q (52H) in the standard systema

This register selects one of four drives, one of (up to) sixteen heads, and controls the two lines which step the heads. There are eight data bits in the register and their specific functions are presented below:

# DRIVE FUNCTION REGISTER

|         | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |         |

|---------|----|----|----|----|----|----|----|----|---------|

| NHDSL8_ | _1 | 1  | 1  | 1  | 1  | 1  | 1  | !_ | _DRVSLO |

| NHDSL4_ |    | _! | 1  | 1  | 1  | 1  | 1_ |    | DRVSL 1 |

| NHDSL2_ |    |    | _! | 1  | 1  | !_ |    |    | NSTEP   |

| NHDSL1_ |    |    |    | _; | 1_ |    |    |    | DIR     |

NHDSL - These are the head select bits. By using four, up to sixteen heads can be selected. On standard drives there are only eight heads. However, there is a model available which has an extra eight heads that are fixed. This allows a user to have 131K of fast access memory on the disk which is independent of the position of the eight moving heads. This model must be specially ordered and customers may have a longer wait for such systems. The relationship between the NHDSL bits and the head selected at the drive is detailed below. Heads numbered 0 through 7 move from track to track, and are present on all models of M26. The fixed heads are numbered 8 through 15, and are usually not present. Heads 8 through 15 should never be selected on a standard drive.

| - | NHDSL8 | NHDSL4 | NHDSL2 | NHDSL1 | HEAD NO. |

|---|--------|--------|--------|--------|----------|

| 1 | 0      | 0      | 0      | 0      | 15       |

| 1 | 0      | 0      | 0      | 1      | 14       |

| i | 0      | 0      | 1 1    | 0      | 13       |

| ŀ | 0      | 0      | 1 1    | - 1    | 12       |

| ł | 0      | 1      | 0      | 0      | 11       |

| ł | 0      | 1      | 1 0    | 1      | 10       |

| ł | 0      | 1      | 1 1    | 0      | 9        |

| ŧ | 0      | 1      | 1      | 1      | 8        |

| l | 1      | 0      | 0      | 0      | 7        |

| 1 | 1      | 0      | 0      | 1      | 6        |

| 1 | 1      | 0      | 1 1    | 0      | 5        |

| 1 | 1      | 0      | 1 1    | 1      | 4 .      |

| i | 1 1    | 1      | 0      | 0      | 3        |

| ı | 1      | 1      | 0      | 1      | 2        |

| ì | 1 1    | 1      | 1 1    | 0      | 1        |

| ı | 1      | 1      | 1 1    | 1 !    | 0        |

# Hardware Level Registers

- DIR This bit controls the direction the read/write heads move when the NSTEP bit is pulsed. DIR must never change when NSTEP makes a transition from 0 to 1. If DIR is 0, the heads will move toward the center of the disk when step pulses are issued. Conversely, when DIR is 1, the heads will move away from the center of the disk. Track 0 is the outermost track on the disk. Track numbers increase as the heads move closer to the center of the disk.

- NSTEP This bit is used to issue step commands to the disk. Its idle state is 1. To issue a step command, NSTEP is brought low and then high. DIR must not change when NSTEP makes the transition from low to high. There are two modes of operation for stepping the heads: buffered and normal. In normal mode, the heads will move at the rate of the incoming NSTEP pulses and the minimum time between successive steps is 1 millesecond. In buffered mode, the step pulses are buffered into a counter at the drive. After the last pulse, the heads will begin stepping toward the appropriate track. The COMPLT bit (of the status register) will go true after the heads arrive at the proper track.

- DRVSL These two bits select one of four drives. The relationship between these bits and the physical drive that is selected is given by the following table:

| ľ  | DRVSL1 | DRVSLO | 1  | DRIVE | NO. |

|----|--------|--------|----|-------|-----|

| 1. |        |        | 1. |       |     |

| 1  | 0      | 0      | 1  | 0     |     |

| 1  | 0      | 1      | 1  | 1     |     |

| 1  | 1      | 0      | 1  | 2     |     |

| 1  | 1      | 1      | 1  | 3     |     |

| 1_ |        |        | 1  |       |     |

When power is first applied to the system the function register is in an unknown state. It is the user's responsibility to write a proper pattern to this port before its output drivers are enabled. In particular, NSTEP should be 1 when the outputs are first enabled.

Register 5 - The controller command port.

Location 121Q (51H) in the standard system.

# Hardware Level Registers

This register is four bits wide and commands are transferred using the low order nibble of the data. The controller will execute six commands: reset the data buffer pointer to the first location of the data area, read a sector header, read a sector of data, write a sector of data, write a sector header, and reset the data buffer pointer to the first location of the header area. There are several more commands which the controller can accept, but these are for test purposes and should NEVER be used in a normal environment. A loss of data on the disk could occur if the user should issue any unlisted command. A detailed explanation of the standard commands is presented below. The command numbers below are also the numeric values to use when issuing commands to the controller through this port.

#### COMMAND O

As explained previously, the controller has a 1024 byte data buffer which is divided into two sections: sector data and sector header information. These two sections share a pointer which is used to address the buffer. Command 0 resets this pointer to the beginning of the data area of the buffer. All commands affect bits in the status registers. Command 0 resets OPDONE, TIMOUT, and SDONE. No other status bits are changed.

#### COMMAND 3

Read a sector header. After receipt of this command, the HALT bit of the main status register is brought false and no further access to the internal data bus is allowed until the command terminates. OPDONE, TIMOUT, SDONE, and RETRY are reset. When the next sector pulse from the drive arrives, the controller reads the four bytes of the header into the 3rd, 4th, 5th, and 6th locations of the sector header area of the buffer. The CRC checksum bytes are compared with the contents of the CRC register. If there was an error in the data transfer, the RETRY bit in the auxiliary status port is set. After the CRC bytes have been checked, the HALT bit is brought back to its true state and the command terminates with OPDONE set.

#### COMMAND 1

This is the read sector command. As before, the first thing that occurs is OPDONE, TIMOUT, RESET, and SDONE are reset. The HALT bit is reset and access to the internal data bus is inhibited. As sector pulses arrive from the drive, the controller scans the sector header and compares it with the FIRST four bytes of the header area of the internal buffer. If the sector header data matches the buffer AND the CRC bytes match the contents of the CRC register, the data in the sector is read into the data area of the internal buffer. The first byte of data is written into the 3rd location of this area in the buffer. Successive bytes are written into successive locations. The next to last byte is written into the first location of the data

area and the last byte from the disk is placed in the second location. After the last byte is read, the controller compares the CRC checksum bytes with the contents of the CRC register. If there is a compare error, the RETRY bit of the auxiliary status register is set and the command terminates with OPDONE set. If the header does not match the pattern in the header area of the buffer, the controller continues to scan successive headers until a match is found (including CRC data) or until 16 index pulses have occured. If no match is found by the 16th index, the TIMOUT bit of the main status register and the RETRY bit of the auxiliary status register are set and the command terminates with OPDONE and HALT being set.

COMMAND 5 This is the write sector command. The sequence of events is exactly the same as with the read sector command up to the point of the actual data transfer. If a match has occured between the header area of the buffer and a sector header, the data area of the internal buffer is written to the sector where the header match took place. The data is transferred starting at the FIRST location of the data area of the buffer. Successive bytes are taken from successive locations. The last byte written to the disk is fetched from the last location in the data area of the buffer. If the header image in the buffer has no counterpart on the current track and head of the disk, the RETRY and TIMOUT bits are set in the status registers after 16 revolutions from the time the command was issued. As before, OPDONE and HALT are also set at the end of the command.

- COMMAND 7 This command writes the first four bytes in the header area of the buffer on a sector header. The header in question is the very first that is encountered after receipt of the command. TIMOUT or RETRY cannot be set by this command. As usual, however, OPDONE and HALT are set at the command's conclusion.

- COMMAND 8 This command resets the internal pointer to the first location of the header area of the controller's data buffer. The other effects of this command are identical to command 0.

Within the four bits allowed by commands, a total of sixteen are possible. However, the user is strongly cautioned NOT to use any except those listed above. If any other commands are issued to the controller, data on the disk could be lost if the WPROT bit in the control register is low. A good practice is to keep WPROT high at all times except during periods when write commands (5 & 7) are in progress.

# CONTROLLER INITIALIZATION

When the system is first powered up the controller should be initialized before starting any operations that involve the disk. Outlined below is just one of several ways that this task can be accomplished.

- 1. Initialize the Drive function register port 122Q. In particular NSTEP must be initialized to 1. If drive 0 is to be selected, a typical value to load this register with is 374Q (FC hex).

- 2. Load the Control register port 120Q with 11Q to enable the outputs of the function register and to write protect the drive.

- 3. Wait for the drive to become ready and then switch the master clock to the drive clock. Also, toggle the WPROT bit to clear any write fault conditions. Finally, turn the run bit on and write protect the drive.

# PREPARING THE CONTROLLER FOR DATA TRANSFER COMMANDS

Before giving the controller a read or a write command, certain tasks should be attended to. These are outlined below:

- 1. Select the proper drive.

- 2. Move the heads to the proper track.

- 3. Select the desired head.

- Load the sector header area of the internal buffer with the proper header information: head number, track number, sector number, and key. This data must be written in the first four bytes of this area of the buffer.

- 5. If data is to be written to the disk, load the data area of the buffer with the desired information from main memory.

The user will find it useful to study carefully the utility software listings at the back of this manual to see an example of how these tasks have been carried out.

#### INTERRUPTS

In the lower left hand corner of the board there are two jumper holes labeled "A" and "B". "A" is driven by the OPDONE bit of the main status register and "B" is driven by the SDONE bit of the auxiliary status register. These two jumper holes can be connected to any of nine interrupt lines of the S-100 bus: VIO - VI7 or PINT. These signals have been brought in from the bus to jumper holes to the right of the "A" and "B" holes and just above the edge connector at the bottom of the board. jumper holes are labeled on the silk screened legend. "A" and "B" can be connected to the same line or, if OPDONE and SDONE should have different priority levels, they can be connected to different interrupt lines. When one or more of these signals are connected to the interrupt lines, interrupts can be generated by the board when transfer operations complete and/or when head motion at the disk completes. Throughput to and from the disk can be greatly enhanced by using these two signals properly.

\* Low Level Hard Disk Drivers. The following routines are the \* lowest level drivers for the hard disk.

\* Written By Bobby Dale Gifford. \* 12/8/80

| 0000                                                             |                                    | HDREV                                                                                                  | EQU                                    | 12                                                                               | ;Revision number                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000                                                              | + =                                | MAXHD                                                                                                  | EQU                                    | 4                                                                                | ;Maximum # of Hard Disk Drives                                                                                                                                                                                                                                                                                                                                          |

| 0050<br>0050<br>0050<br>0051<br>00051<br>00001<br>00004<br>00008 |                                    | HDORG HDSTAT HDCNTL HDDATA HDFUNC HDCMND HDRESLT RETRY TKZERO OPDONE COMPLT TMOUT WFAULT               | EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU | 50H HDORG HDORG HDORG+3 HDORG+2 HDORG+1 HDORG+1 2 1 2 1 2 4 8 10H                | ;Hard Disk Controller origin ;Hard Disk Status ;Hard Disk Control ;Hard Disk Data ;Hard Disk Function ;Hard Disk Command ;Hard Disk Result ;Retry bit of result ;Track zero bit of status ;Operaction done bit of status ;Complete bit of status ;Time out bit of status ;Write fault bit of status                                                                     |

| 0020<br>0040<br>0004<br>0007<br>0007<br>0007<br>0007<br>0007     |                                    | DRVRDY INDEX PSTEP NSTEP HDRLEN SECLEN WENABL WRESET SCENBL DSKCLK MDIR NULL IDBUFF ISBUFF RSECT WSECT | E E E E E E E E E E E E E E E E E E E  | 20H<br>40H<br>4<br>0FBH<br>4<br>512<br>0FH<br>0BH<br>5<br>7<br>0F7H<br>0FCH<br>0 | ;Drive ready bit of status ;Index bit of status ;Step bit of function ;Step bit mask of function ;Sector header length ;Sector data length ;Write enable ;Write reset of function ;Controller control ;Disk clock for control ;Direction mask for function ;Null command ;Initialize data command ;Initialize header command ;Read sector command ;Write sector command |

| 0015                                                             | =                                  | SECCNT                                                                                                 | EQU                                    | 21                                                                               | ;Sectors per track<br>;32 for M26<br>;21 for M10 & M20                                                                                                                                                                                                                                                                                                                  |

| 0100                                                             |                                    |                                                                                                        | ORG                                    | 100H                                                                             |                                                                                                                                                                                                                                                                                                                                                                         |

| 0103<br>0105                                                     | 317603<br>0E00<br>CD7603<br>CD7903 |                                                                                                        | LXI<br>MVI<br>CALL<br>CALL             | SP, STACK<br>C, O<br>SETDRV<br>HOME                                              |                                                                                                                                                                                                                                                                                                                                                                         |

010B 014401

010E CD8203

0113 CD7C03

0111 0E00

LXI

CALL

MVI

CALL

LOOP

B, BXX

C,0

SETDMA

SETTRK

| - 4                                                                                                  |                                    |          |                                                                              |                                                                                                         |

|------------------------------------------------------------------------------------------------------|------------------------------------|----------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 0118<br>011D<br>0120<br>0122<br>0125<br>0128<br>0128<br>012B<br>012E<br>0130<br>0133<br>0135<br>0138 | CD7F03<br>0E80<br>CD8803<br>CD7B04 |          | MVI CALL MVI CALL CALL NOP MVI CALL MVI CALL MVI CALL MVI CALL MVI CALL CALL | C, 0 SETHEAD C, 1 SETSEC C, 80H SETKEY HDREAD C, 200 SETTRK C, 0 SETHEAD C, 1 SETSEC C, 0 SETKEY HDREAD |